GZIP/ZLIB/Deflate 数据压缩内核

该内核接收未压缩的输入文件并生成压缩文件。无需对压缩文件进行后期处理,因为内核用适当的数据头和脚注封装了压缩数据有效载荷。可以对输入文件进行分段,并且可以将不同文件的分段在内核的输入处进行交织。

该内核的灵活架构可对其压缩效率,吞吐量和延迟进行微调,以适应最终应用的需求。甚至在低成本FPGA中,也可以实现超过100 Gbps的吞吐量,并且延迟可以只有几十个时钟周期。

ZipAccel-C提供的压缩效率实际上等同于当今流行的基于deflate的软件应用程序。通过附带的软件模型以及我们数据压缩专家团队的支持,能够分析处理速度与压缩效率的关系,以实现在特定系统中两者的最佳平衡。

ZipAccel-C的设计易于使用和集成。它独立运行,将主机CPU从繁重的数据压缩任务中解脱出来,还可以从加密压缩流的加密任务中解脱出来。流数据接口和可选的AMBA总线接口使SoC集成得到简化。

工艺映射非常简单,因为设计是可扫描的,无微码的,并且使用易于替换的通用存储模型。存储模块可以选择支持错误校验码(ECC),以简化实现企业级的可靠性要求。此外,输入文件分段可以限制文件间延迟,并帮助用户实现服务质量(QoS)目标。该内核已经过严格的验证,并已在众多商业产品中进行了量产验证。

查看 GZIP/ZLIB/Deflate 数据压缩内核 详细介绍:

- 查看 GZIP/ZLIB/Deflate 数据压缩内核 完整数据手册

- 联系 GZIP/ZLIB/Deflate 数据压缩内核 供应商

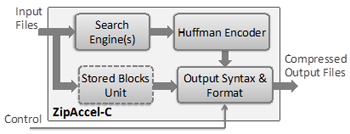

Block Diagram of the GZIP/ZLIB/Deflate 数据压缩内核