You are here:

Graphics Processor Overlay IP Core

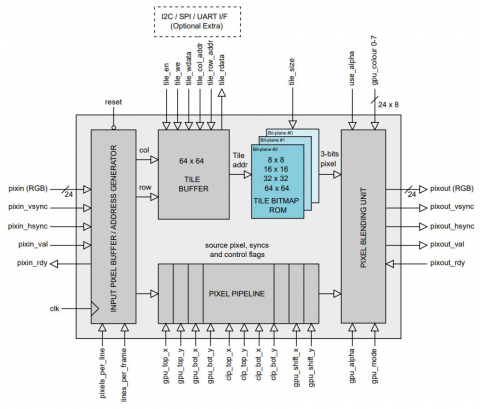

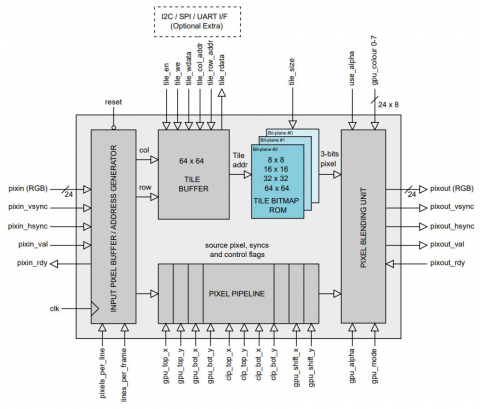

The GPU_OVERLAY IP Core (Figure 1) is a highly versatile on-screen display processor that allows high-quality anti-aliased bitmap graphics and text to be inserted over RGB video. The module supports a wide range of graphics effects and the programming interface is very simple to use. The bitmap overlay is partitioned into an array of tiles which are stored in a local tile buffer memory. There are four tile sizes available which are either: 8x16, 16x32, 32x64 or 64x128.

The tiles in the buffer are displayed in a graphics window which may be positioned anywhere within the display area. Bitmaps for each tile are defined in a ROM which can contain up to 128 different bitmaps stored over three bit-planes. Depending on the chosen graphics mode, the 3- bits per pixel may be used to select one colour from a palette of eight, eight levels of alpha transparency or seven colours on a transparent background. There is also a feature to highlight a tile with a background colour. This is especially useful for interactive text-based menus and lists where the user has to select an option.

Pixels flow in and out of the overlay module in accordance with a simple streaming (valid/ready) protocol. Pixels and syncs are sampled at the module inputs on a rising clock-edge when pixin_val is high and pixin_rdy is high. Likewise, pixels and syncs are transferred out of the module on a rising clock-edge when pixout_val and pixout_rdy are asserted high. The streaming protocol allows both input and output interfaces to be stalled independently.

The streaming protocol is very versatile and permits any number of GPU overlay modules to be cascaded in series. By placing more than one module together, the user is able to achieve more complex text and graphics displays with different fonts and colours.

The tiles in the buffer are displayed in a graphics window which may be positioned anywhere within the display area. Bitmaps for each tile are defined in a ROM which can contain up to 128 different bitmaps stored over three bit-planes. Depending on the chosen graphics mode, the 3- bits per pixel may be used to select one colour from a palette of eight, eight levels of alpha transparency or seven colours on a transparent background. There is also a feature to highlight a tile with a background colour. This is especially useful for interactive text-based menus and lists where the user has to select an option.

Pixels flow in and out of the overlay module in accordance with a simple streaming (valid/ready) protocol. Pixels and syncs are sampled at the module inputs on a rising clock-edge when pixin_val is high and pixin_rdy is high. Likewise, pixels and syncs are transferred out of the module on a rising clock-edge when pixout_val and pixout_rdy are asserted high. The streaming protocol allows both input and output interfaces to be stalled independently.

The streaming protocol is very versatile and permits any number of GPU overlay modules to be cascaded in series. By placing more than one module together, the user is able to achieve more complex text and graphics displays with different fonts and colours.

查看 Graphics Processor Overlay IP Core 详细介绍:

- 查看 Graphics Processor Overlay IP Core 完整数据手册

- 联系 Graphics Processor Overlay IP Core 供应商

Block Diagram of the Graphics Processor Overlay IP Core

GPU IP

- 3D-like multicore GPU

- Ultra-low-power RISC-V based GPU Processor

- High-performance 2D (sprite graphics) GPU IP combining high pixel processing capacity and minimum gate count.

- 2D (vector graphics) GPU IP Further advanced architecture for minimized CPU load and increased pixel performance in vector processing

- 2D (vector graphics) & 3D GPU IP A GPU IP combining 3D and 2D rendering features with high performance, low power consumption, and minimum CPU load

- Shader architecture type 3D GPU Integrating the OpenVG 1.1 hardware processing pipeline