Bluetooth low energy v5.4 Baseband Controller, Protocol Software Stack and Profiles IP

You are here:

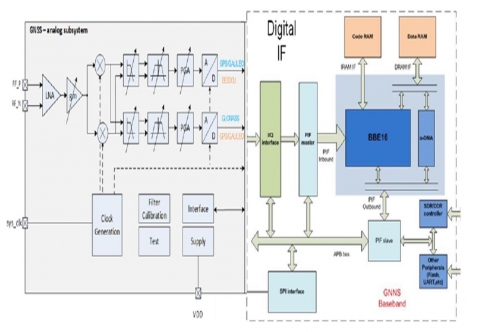

GNSS 软件接收器(GPS、Galileo、GLONASS、Beidou3、QZSS、SBAS)IP

这个软件接收器是下一代全球导航卫星系统(GNSS)接收器,涵盖GPS和SBAS卫星系统,通过在软件中完全执行接收器的主要任务(搜索、跟踪和定位)来完全取代现有的硬件接收器解决方案。这个高性能接收器可根据客户需求进行定制,适用于各种DSP和处理器,符合低功耗、高性能和小尺寸的物联网(IoT)细分市场

查看 GNSS 软件接收器(GPS、Galileo、GLONASS、Beidou3、QZSS、SBAS)IP 详细介绍:

- 查看 GNSS 软件接收器(GPS、Galileo、GLONASS、Beidou3、QZSS、SBAS)IP 完整数据手册

- 联系 GNSS 软件接收器(GPS、Galileo、GLONASS、Beidou3、QZSS、SBAS)IP 供应商