90nm OTP Non Volatile Memory for Standard CMOS Logic Process

General Purpose Fractional-N PLLs

Perceptia’s second generation pPLL02F family is available on technologies from 5nm to 40nm and across multiple foundry partners. We are continually expanding the range of technologies where it is silicon proven and can quickly port it to other technologies or foundries upon request.

To give SoC designers the maximum flexibility in building complex multi-domain clock systems, pPLL02F is very small (< 0.005 sq mm) and low power (< 1.7mW in GF22FDX). It is well suited to applications with many clock domains where each is driven by their own PLL. To simplify system design, PLL02F has an integrated power supply regulator which allows multiple instances of PLL02F to share common power supplies. Alternatively instances of pPLL02F can share supplies with the blocks that use its output clock.

pPLL02F integrates easily into any SoC design and includes all the views and models required by back end flows.

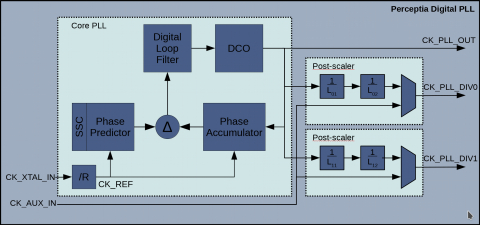

The pPLL02F is built using Perceptia’s second generation all digital PLL technology. This robust technology delivers identical performance across many processes, regardless of PVT conditions. It consumes a small fraction of the area of an analog PLL whilst maintaining comparable performance.

pPLL02F can be used as an integer-N PLL or as a fractional-N PLL. The fractional-N mode provides a high flexibility to choose the best combination of input and output clock frequencies at the system level.

Perceptia further provides integration support and offers customization and migration services.

查看 General Purpose Fractional-N PLLs 详细介绍:

- 查看 General Purpose Fractional-N PLLs 完整数据手册

- 联系 General Purpose Fractional-N PLLs 供应商

Block Diagram of the General Purpose Fractional-N PLLs

pll IP

- TSMC CLN7FF 7nm Clock Generator PLL - 800MHz-4000MHz

- TSMC GF Intel Samsung Deskew Frequency Synthesizer PLL

- TSMC GF Intel Samsung Fractional-N Frequency Synthesizer PLL

- TSMC GF Intel Samsung Integer-N Frequency Synthesizer PLL

- Jitter Cleaner PLL Digital Loop Filter

- TSMC Intel 32kHz Low-bandwidth Frequency Synthesizer PLL