You are here:

GbE (10/100 Base-T) PHY IP,经过硅验证的 UMC 40LP

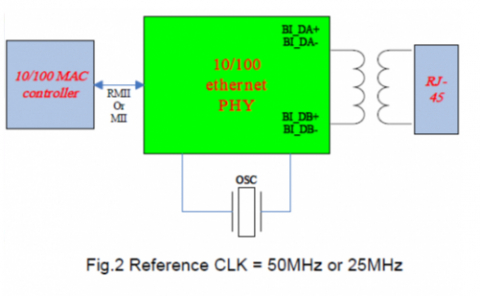

这个以太网PHY IP符合IEEE 802.3u标准规范,是单端口以太网物理层收发器,在以10BASE-Te和100BASE-TX模式运行时具有低功耗的特性。EPHY通过千兆媒体独立接口(GMII)连接到媒体访问控制层(MAC),在媒体方面,它为10BASE-Te以太网提供一个直接接口到UTP5/UTP3电缆,或为100BASE-TX快速以太网提供非屏蔽双绞线5类电缆(UTP5)。以太网PHY采用的CMOS技术具有低功耗和高性能的特点,具有符合IEEE802.3u标准规范规定的100BASE-TX物理层功能(TP-PMD,仅100BASE-TX),物理编码子层(PCS)、物理介质附着层(PMA)和双绞线物理介质依赖子层。此外,EPHY有一个强大的自动协商功能,使用自动媒体速度/双工和协议选择匹配

查看 GbE (10/100 Base-T) PHY IP,经过硅验证的 UMC 40LP 详细介绍:

- 查看 GbE (10/100 Base-T) PHY IP,经过硅验证的 UMC 40LP 完整数据手册

- 联系 GbE (10/100 Base-T) PHY IP,经过硅验证的 UMC 40LP 供应商