You are here:

Four Channel (4CH) LVDS Serializer in Samsung 28FDSOI

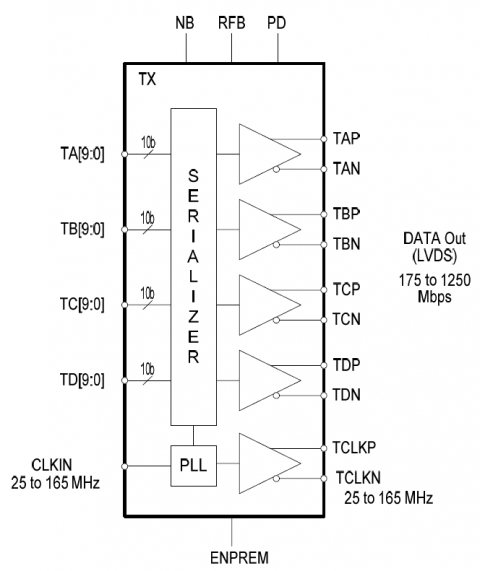

The 28FDSOI-LVDS-4CH-TX-1250-PLL is a high performance 4-channel LVDS Serializer implemented using digital CMOS technology. Both the serial and parallel data are organized into four channels. The parallel data is 7/10 bits wide per channel. The input clock is 25MHz to 165MHz. The serializer is highly integrated and requires no external components. It employs optional pre-emphasis to enable transmission over a longer distance while achieving low BER. The circuit is designed in a modular fashion and desensitized to process variations. This facilitates process migration, and results in a robust design.

查看 Four Channel (4CH) LVDS Serializer in Samsung 28FDSOI 详细介绍:

- 查看 Four Channel (4CH) LVDS Serializer in Samsung 28FDSOI 完整数据手册

- 联系 Four Channel (4CH) LVDS Serializer in Samsung 28FDSOI 供应商