Performance Efficiency AI Accelerator for Mobile and Edge Devices

You are here:

Floating-point (IEEE 754) IP based on Arria 10 and Stratix 10 FPGAs

This circuit uses Altera’s new Arria and Stratix 10 FPGAs with hardwired support for floating-point operations (IEEE754). Since Centar's FFT engine consists only of floating-point primitives (add, accumulate, multiply), there is a substantial reduction in LUT and register usage. Thus, high precision FFTs no longer use substantial FPGA resources, e.g., x2 and x6 less LUT/register usage compared to Centar's and Altera's fixed-point FFT IEEE754 implementation. Also, our Arria 10 versions use x2 fewer ALMs than Altera's. Finally, the locality, simplicity and regularity of the processing core keeps interconnect delays lower than cell delays, leading to reduced power dissipation and much higher throughputs.

查看 Floating-point (IEEE 754) IP based on Arria 10 and Stratix 10 FPGAs 详细介绍:

- 查看 Floating-point (IEEE 754) IP based on Arria 10 and Stratix 10 FPGAs 完整数据手册

- 联系 Floating-point (IEEE 754) IP based on Arria 10 and Stratix 10 FPGAs 供应商

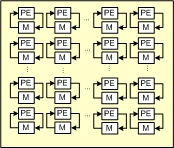

Block Diagram of the Floating-point (IEEE 754) IP based on Arria 10 and Stratix 10 FPGAs