FlexNoC 5 互联 IP-兼顾物理感知的片上网络 IP

全球顶级的半导体设计团队利用全球一流的片上结构作为其芯片的片上通信主干,从而应对增长最快的市场。

最新一代 FlexNoC 5 互连及其集成的兼顾物理感知技术为布局和布线团队提供了更好的起点,同时减少了互连面积和功耗。与手动物理迭代相比,FlexNoC 5 的周转时间缩短了 5 倍。

在 ASIC 设计中结合使用 FlexNoC 和 Ncore IP 可提供无与伦比的性能优化、可扩展性和系统集成,从而实现强大的缓存一致性、高效通信和灵活性,实现市场差异化并加快上市速度。

查看 FlexNoC 5 互联 IP-兼顾物理感知的片上网络 IP 详细介绍:

- 查看 FlexNoC 5 互联 IP-兼顾物理感知的片上网络 IP 完整数据手册

- 联系 FlexNoC 5 互联 IP-兼顾物理感知的片上网络 IP 供应商

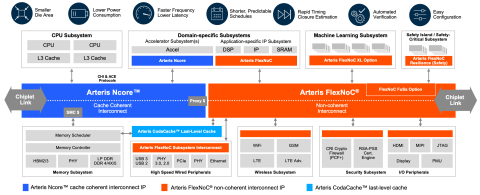

Block Diagram of the FlexNoC 5 互联 IP-兼顾物理感知的片上网络 IP

Video Demo of the FlexNoC 5 互联 IP-兼顾物理感知的片上网络 IP

Understanding how on-chip interconnect and DDR memory controller configurations impact the system performance, power and cost of multicore SoCs requires deep visibility. Sponsored by Synopsys and Arteris, this webinar illustrates how virtual prototyping tools and high-level architecture models provide SoC architects with the deep, system-level analysis they need to configure and optimize Quality-of-Service (QoS) features earlier in the design cycle.