You are here:

FIR 滤波器生成器

有限脉冲响应( FIR )滤波器实现输入数据序列与存储在存储器中的滤波器脉冲响应的卷积(即所需频率响应的离散傅立叶变换的逆运算)。卷积公式如下所示

其中yn是第n个采样的滤波器输出,xn-i是过去i个采样的滤波器输入,hi是第i个滤波器的脉冲响应。

莱迪思FIR (有限脉冲响应)滤波器IP核是一个可广泛配置、多通道的FIR滤波器,采用莱迪思器件中的高性能sysDSP™模块来实现。除了单速率滤波器,IP核还支持各种多相抽取和内插滤波器。利用率与吞吐量之间的权衡可通过指定滤波器所使用的乘法器的数量来进行控制。FIR滤波器IP核支持多达256个通道,且每个有高达2,048个抽头。输入数据、系数和输出数据宽度都可以在很大范围内进行配置。IP核使用全内部精度,同时允许可变的输出精度,拥有多种saturation(饱和)和rounding(四舍五入)选择。滤波器的系数可以通过输入端口在生成时间和/或在运行时可重载入时指定。

基于高性能ECP3 DSP的滤波器设计

莱迪思已经开发的下面这些参考设计重点介绍了LatticeECP3 FPGA强大的DSP功能。

* 直接64-Tap FIR滤波器:在直接FIR滤波器中,输入采样进入一个移位寄存器队列,并且每个移位寄存器连接到一个乘法器。乘法器的乘积相加得到FIR滤波器的输出采样。这个例子说明了一个64-Tap FIR滤波器,使用了LatticeECP3 FPGA中的16个sysDSP模块和大约512个slice。

* 采用梯形结构的128-Tap长非对称型滤波器:采用梯形结构,FIR滤波器分成几块,每块具有相同的系数设置,就好像它是一个单独、连续的滤波器链。在梯形结构中,不再是将第一部分的移位数据和输出结果连接到下一部分的相应输入,而是将第一部分的输入加上延迟输入到第二部分,并将第一部分的总和输出加上延迟与第二部分的总和输出相加。

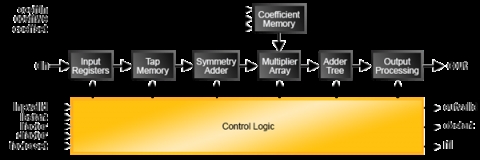

* 采用梯形结构的256-Tap长对称型滤波器:对于大多数FIR滤波器来说脉冲响应是对称的。这种对称性通常可以用来减少计算量并产生低面积高效的滤波器实现。与使用非对称系数相比,使用对称系数的相似的滤波器可以少用一半数量的乘法器。对称系数的实现如下图所示。256-Tap长对称型滤波器示例仅使用了32个sysDSP slice、2个EBR和3.5K slice。

* 多相内插FIR滤波器设计:多相内插滤波器实现了高计算效率的1到P个插值的滤波器,其中P是大于1的整数。下面的例子是使用了128个抽头的16插值滤波器设计。这需要8个多相滤波器(子滤波器),每个有16个系数。

其中yn是第n个采样的滤波器输出,xn-i是过去i个采样的滤波器输入,hi是第i个滤波器的脉冲响应。

莱迪思FIR (有限脉冲响应)滤波器IP核是一个可广泛配置、多通道的FIR滤波器,采用莱迪思器件中的高性能sysDSP™模块来实现。除了单速率滤波器,IP核还支持各种多相抽取和内插滤波器。利用率与吞吐量之间的权衡可通过指定滤波器所使用的乘法器的数量来进行控制。FIR滤波器IP核支持多达256个通道,且每个有高达2,048个抽头。输入数据、系数和输出数据宽度都可以在很大范围内进行配置。IP核使用全内部精度,同时允许可变的输出精度,拥有多种saturation(饱和)和rounding(四舍五入)选择。滤波器的系数可以通过输入端口在生成时间和/或在运行时可重载入时指定。

基于高性能ECP3 DSP的滤波器设计

莱迪思已经开发的下面这些参考设计重点介绍了LatticeECP3 FPGA强大的DSP功能。

* 直接64-Tap FIR滤波器:在直接FIR滤波器中,输入采样进入一个移位寄存器队列,并且每个移位寄存器连接到一个乘法器。乘法器的乘积相加得到FIR滤波器的输出采样。这个例子说明了一个64-Tap FIR滤波器,使用了LatticeECP3 FPGA中的16个sysDSP模块和大约512个slice。

* 采用梯形结构的128-Tap长非对称型滤波器:采用梯形结构,FIR滤波器分成几块,每块具有相同的系数设置,就好像它是一个单独、连续的滤波器链。在梯形结构中,不再是将第一部分的移位数据和输出结果连接到下一部分的相应输入,而是将第一部分的输入加上延迟输入到第二部分,并将第一部分的总和输出加上延迟与第二部分的总和输出相加。

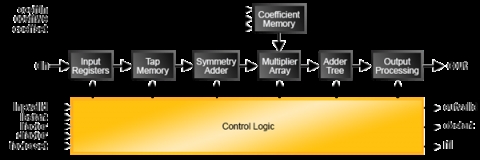

* 采用梯形结构的256-Tap长对称型滤波器:对于大多数FIR滤波器来说脉冲响应是对称的。这种对称性通常可以用来减少计算量并产生低面积高效的滤波器实现。与使用非对称系数相比,使用对称系数的相似的滤波器可以少用一半数量的乘法器。对称系数的实现如下图所示。256-Tap长对称型滤波器示例仅使用了32个sysDSP slice、2个EBR和3.5K slice。

* 多相内插FIR滤波器设计:多相内插滤波器实现了高计算效率的1到P个插值的滤波器,其中P是大于1的整数。下面的例子是使用了128个抽头的16插值滤波器设计。这需要8个多相滤波器(子滤波器),每个有16个系数。

查看 FIR 滤波器生成器 详细介绍:

- 查看 FIR 滤波器生成器 完整数据手册

- 联系 FIR 滤波器生成器 供应商

Block Diagram of the FIR 滤波器生成器

FPGA IP

- RT-630-FPGA Hardware Root of Trust Security Processor for Cloud/AI/ML SoC FIPS-140

- Complete USB Type-C Power Delivery PHY, RTL, and Software

- Ethernet TSN Switch IP Core - Efficient and Massively Customizable

- CXL 2.0 Agilex FPGA Acclerator Card

- PCIe Gen3 to SRIO Gen3 Bridge (FPGA)

- 65nm/40nm Low Power eFPGA IP and Open Source FPGA Software