MIPI CSI DSI C-PHY IP for TSMC (5nm, 6/7nm, 12/16nm, 22nm, 28nm, 40nm)

You are here:

Extended MIPI CSI2 Serial Video Receiver For FPGA

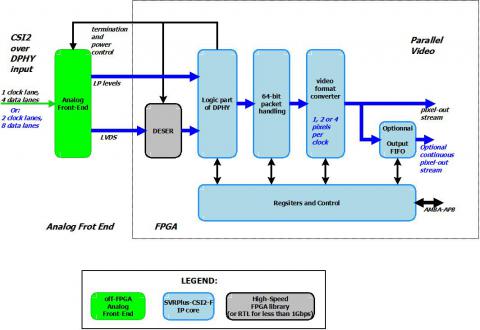

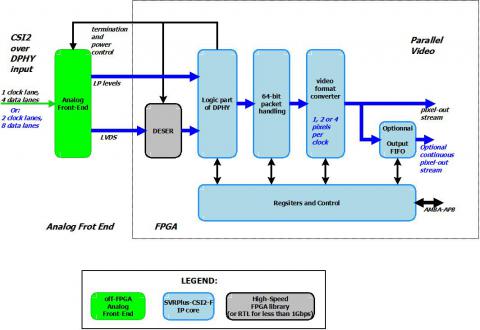

The Extended MIPI CSI2 Serial Video Receiver IP core is designed to support those trends, and, at the same time, work with a relatively slow clock rate, processing several pixels per clock.

The Extended MIPI CSI2 Serial Video Receiver IP core has an internal 64-bit bus. With this bus width, 10Gbps can be handled by a reasonable167MHz clock.

The output path of the The Extended MIPI CSI2 Serial Video Receiver IP core can handle 1, 2 or 4 pixels in parallel. Image sensors which generate, for example, 12M * 60 fps = 720M pixels per second, can be handled by the SVRPlus-CSI2-F driven by a 180MHz clock, if the PARALLEL_PIXELS compilation switch is set to 4.

The Extended MIPI CSI2 Serial Video Receiver IP core can handle up to 8 data lanes, with one or two clock lanes, and at up to 1.5Gbps per lane. If extended CSI2 is not required, the customer can save gate count and off-FPGA circuits by setting the EIGHT_LANES compilation switch to NO.

The Extended MIPI CSI2 Serial Video Receiver IP core has an internal 64-bit bus. With this bus width, 10Gbps can be handled by a reasonable167MHz clock.

The output path of the The Extended MIPI CSI2 Serial Video Receiver IP core can handle 1, 2 or 4 pixels in parallel. Image sensors which generate, for example, 12M * 60 fps = 720M pixels per second, can be handled by the SVRPlus-CSI2-F driven by a 180MHz clock, if the PARALLEL_PIXELS compilation switch is set to 4.

The Extended MIPI CSI2 Serial Video Receiver IP core can handle up to 8 data lanes, with one or two clock lanes, and at up to 1.5Gbps per lane. If extended CSI2 is not required, the customer can save gate count and off-FPGA circuits by setting the EIGHT_LANES compilation switch to NO.

查看 Extended MIPI CSI2 Serial Video Receiver, 64 bits, 8 data lanes, 4 pixels/clock 详细介绍:

- 查看 Extended MIPI CSI2 Serial Video Receiver, 64 bits, 8 data lanes, 4 pixels/clock 完整数据手册

- 联系 Extended MIPI CSI2 Serial Video Receiver, 64 bits, 8 data lanes, 4 pixels/clock 供应商

Block Diagram of the Extended MIPI CSI2 Serial Video Receiver, 64 bits, 8 data lanes, 4 pixels/clock

MIPI CSI2 Receiver IP

- MIPI CSI-2 controller Receiver v 2.1, Compatible with MIPI C-PHY v1.2 & DPHY v2.1.

- Very compact (500 LUTs) Camera Sensor Receiver Interface Converting from MIPI CSI-2 to AXI4-Stream Video Standard

- MIPI D-PHY CSI-2 RX (Receiver) in Samsung 28FDSOI

- MIPI D-PHY CSI-2 RX+ (Receiver) IP in TSMC 28HPM

- 2.5Gbps Per Lane MIPI-CSI2 Compliant Serial Video Receiver

- MIPI D-PHY CSI-2 RX+ (Receiver) IP in TSMC 40LP