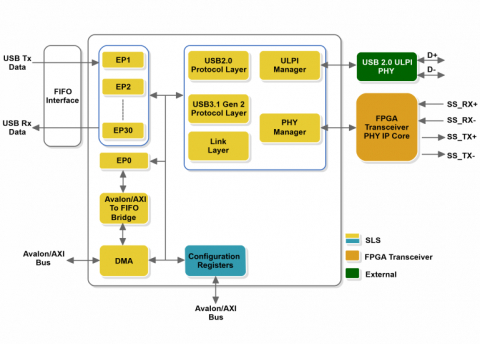

USB 10Gbps Device Controller

It has been designed to provide simplicity and flexibility along with highest throughput around 8.5Gbps. Avalon/AXI interface allows to manage the control transfer using software, provides flexibility, while FIFO interface allows to transfer the data over non-control endpoint ensuring highest throughput.

查看 USB 10Gbps Device Controller 详细介绍:

- 查看 USB 10Gbps Device Controller 完整数据手册

- 联系 USB 10Gbps Device Controller 供应商

Block Diagram of the USB 10Gbps Device Controller

Video Demo of the USB 10Gbps Device Controller

This video showcase the performance achieved for the eUSB 3.1 Gen 2 Device Controller IP Core on Arria 10 GX development kit.