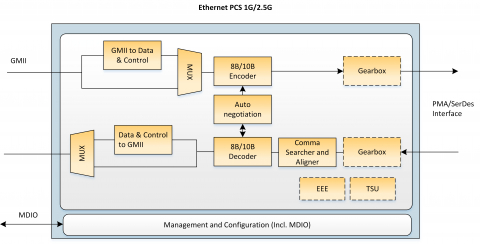

Ethernet PCS 1G/2.5G

The IP-core is verified using advanced methodologies for RTL design, verification, HW verification and interoperability testing. It has been optimized for size and is a highly tested solution that will fast track any project.

查看 Ethernet PCS 1G/2.5G 详细介绍:

- 查看 Ethernet PCS 1G/2.5G 完整数据手册

- 联系 Ethernet PCS 1G/2.5G 供应商

Block Diagram of the Ethernet PCS 1G/2.5G

Ethernet IP

- 10G-100G MACsec Security Module for Ethernet

- 224G Ethernet PHY in TSMC (N3E, N2P)

- 112G Ethernet PHY in TSMC (N7, N6, N5, N3P)

- Multi-protocol SerDes PMA - PCIe1 PCIe2 PCIe3 PCIe4 PCIe5 and more

- 1-56/112G Multi-protocol Serdes (Interlaken, JESD204, CPRI, Ethernet, OIF/CEI)

- PCIe Gen 6 SERDES IP - supports up to 112G LR ethernet with low power and latency