90nm OTP Non Volatile Memory for Standard CMOS Logic Process

Ethernet PCS 100G

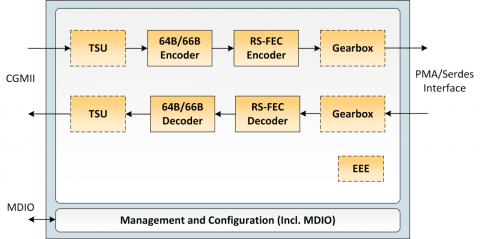

The Ethernet PCS IP supports 100G line rates, however other Ethernet PCS speeds are available, such as 1G/2.5G and 10G/25G. The IP provides an interface between the Media Access Control (MAC) and Physical Medium Attachment (PMA) through a 4 lane parallel interface and offers a CGMII interface on the other side.

The PCS IP core is verified using advanced methodologies for RTL design, verification, HW verification and interoperability testing. It has been optimized for size and is a highly tested solution that will fast track any project.

查看 Ethernet PCS 100G 详细介绍:

- 查看 Ethernet PCS 100G 完整数据手册

- 联系 Ethernet PCS 100G 供应商

Block Diagram of the Ethernet PCS 100G

Ethernet IP

- 10G-100G MACsec Security Module for Ethernet

- 224G Ethernet PHY in TSMC (N3E, N2P)

- 112G Ethernet PHY in TSMC (N7, N6, N5, N3P)

- Multi-protocol SerDes PMA - PCIe1 PCIe2 PCIe3 PCIe4 PCIe5 and more

- 1-56/112G Multi-protocol Serdes (Interlaken, JESD204, CPRI, Ethernet, OIF/CEI)

- PCIe Gen 6 SERDES IP - supports up to 112G LR ethernet with low power and latency