You are here:

Ethernet 1G/10G flexiMAC MACO Core

The LatticeSCM Ethernet flexiMAC™ MACO™ IP core is a flexible packet framer and parser that can implement Layer2 (data link layer or MAC) functionality for various standards. The flexiMAC functionality complements the Layer1 (physical layer) multi-protocol functionality of the LatticeSCM Physical Coding Sublayer (PCS) and is implemented in MACO hard logic. This yields a complete Layer1/Layer2 solution for 1/10Gb Ethernet standards.

The flexiMAC core assists the FPGA designer’s efforts by providing pretested, reusable functions that can be easily plugged in, freeing designers to focus on their unique system architecture. These blocks eliminate the need to “re-invent the wheel,” by providing either an industry-standard Layer 2 flexible packet framer and parser or a Layer 1 multi-protocol functionality of the Physical Coding Sublayer (PCS) module. This proven core is optimized utilizing the LatticeSCM device’s MACO architecture, resulting in fast, small cores that utilize the latest architecture to its fullest.

Software Requirements

* ispLEVER version 7.0 or later

* MACO design kit

* MACO license file

The flexiMAC core assists the FPGA designer’s efforts by providing pretested, reusable functions that can be easily plugged in, freeing designers to focus on their unique system architecture. These blocks eliminate the need to “re-invent the wheel,” by providing either an industry-standard Layer 2 flexible packet framer and parser or a Layer 1 multi-protocol functionality of the Physical Coding Sublayer (PCS) module. This proven core is optimized utilizing the LatticeSCM device’s MACO architecture, resulting in fast, small cores that utilize the latest architecture to its fullest.

Software Requirements

* ispLEVER version 7.0 or later

* MACO design kit

* MACO license file

查看 Ethernet 1G/10G flexiMAC MACO Core 详细介绍:

- 查看 Ethernet 1G/10G flexiMAC MACO Core 完整数据手册

- 联系 Ethernet 1G/10G flexiMAC MACO Core 供应商

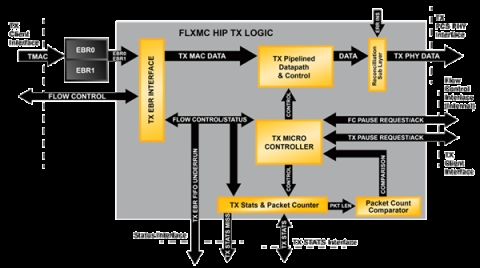

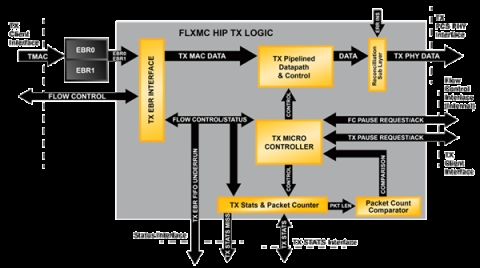

Block Diagram of the Ethernet 1G/10G flexiMAC MACO Core

FPGA IP

- RT-630-FPGA Hardware Root of Trust Security Processor for Cloud/AI/ML SoC FIPS-140

- Complete USB Type-C Power Delivery PHY, RTL, and Software

- Ethernet TSN Switch IP Core - Efficient and Massively Customizable

- CXL 2.0 Agilex FPGA Acclerator Card

- PCIe Gen3 to SRIO Gen3 Bridge (FPGA)

- 65nm/40nm Low Power eFPGA IP and Open Source FPGA Software