You are here:

Error Detection and Correction

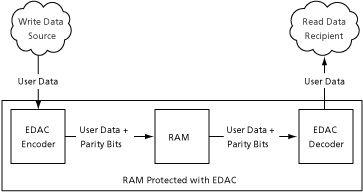

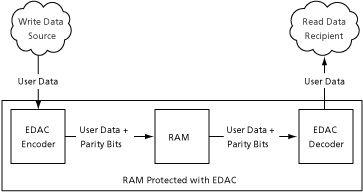

CoreEDAC is an RTL generator that produces an Microsemi FPGA-optimized error detection and correction (EDAC) core. In many applications, storage elements like SRAM are susceptible to soft (transient) errors caused by heavy ions. These errors can be detected and corrected by employing Error Correction Codes (ECCs). CoreEDAC uses ECCs to incorporate redundancy in data forming codewords that are stored in memory. When recovering data, CoreEDAC first determines if a message read from the RAM is valid. If an error is detected, the decoder finds a valid message that is most similar to the one read and corrects the error.

The core can generate EDAC circuitry for both internal (on-chip) and external RAM blocks. For ease of use, the core enables a user to generate the logic integrated with an on-chip RAM.

The core can generate EDAC circuitry for both internal (on-chip) and external RAM blocks. For ease of use, the core enables a user to generate the logic integrated with an on-chip RAM.

查看 Error Detection and Correction 详细介绍:

- 查看 Error Detection and Correction 完整数据手册

- 联系 Error Detection and Correction 供应商

Block Diagram of the Error Detection and Correction