You are here:

eMMC 5.1 HS400 PHY and I/O Pads in TSMC 28HPM-NS

Arasan provides a HS400 compatible PHY that customers can integrate with the HS400 I/O PADs. It is designed to optimize I/O performance with a core voltage of 1.1V and I/O voltage of 1.8/3.3V in the TSMC 28nmHPM process.

These I/O PADs are compliant with the eMMC 5.1 HS400 specification for use in TSMC’s 28nm HPM process. The I/O PADs integrate seamlessly with Arasan’s eMMC 5.1 host controller IP. These PADs address the need for applications requiring high speed as well as low leakage power. eMMC 5.1 HS400 implementation requires a hard PHY for aligning clock edges.

Arasan’s eMMC Total IP which includes the eMMC Controller IP and the eMMC PHY IP have achieved the Automotive Safety Integrity Level B, the architectural metrics SPFM (Single Point Fault Metric) and LFM (Latent Fault Metric) certification, allowing customers to create ISO 26262-compliant SoCs for ADAS and autonomous driving applications.

These I/O PADs are compliant with the eMMC 5.1 HS400 specification for use in TSMC’s 28nm HPM process. The I/O PADs integrate seamlessly with Arasan’s eMMC 5.1 host controller IP. These PADs address the need for applications requiring high speed as well as low leakage power. eMMC 5.1 HS400 implementation requires a hard PHY for aligning clock edges.

Arasan’s eMMC Total IP which includes the eMMC Controller IP and the eMMC PHY IP have achieved the Automotive Safety Integrity Level B, the architectural metrics SPFM (Single Point Fault Metric) and LFM (Latent Fault Metric) certification, allowing customers to create ISO 26262-compliant SoCs for ADAS and autonomous driving applications.

查看 eMMC 5.1 HS400 PHY and I/O Pads in TSMC 28HPM-NS 详细介绍:

- 查看 eMMC 5.1 HS400 PHY and I/O Pads in TSMC 28HPM-NS 完整数据手册

- 联系 eMMC 5.1 HS400 PHY and I/O Pads in TSMC 28HPM-NS 供应商

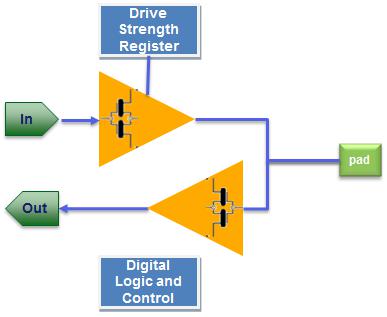

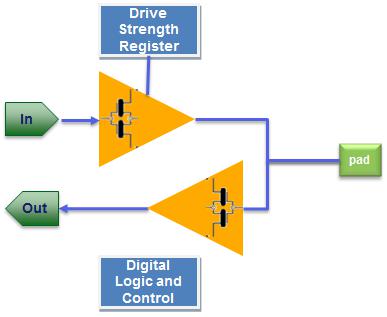

Block Diagram of the eMMC 5.1 HS400 PHY and I/O Pads in TSMC 28HPM-NS