Bluetooth low energy v5.4 Baseband Controller, Protocol Software Stack and Profiles IP

You are here:

动态Reed-Solomon解码器

Reed-Solomon 码用来执行前向纠错(FEC)。 FEC旨在数据传输之前引入了受控的冗余,允许在接收机中进行纠错。冗余数据(检查符号)与原始数据一起传送到接收机。Reed-Solomon解码器用于接收机,以纠正任何传输错误。这种类型的错误纠正被广泛应用于数据通信应用,如数字视频广播(DVB)和光载波(即OC-192)。

莱迪思的动态Reed-Solomon解码器 IP 符合几个行业标准,包括近期的IEEE 802.16-2004,可自定义配置,以支持其他非标准应用。该解码器支持很大范围的符号宽度,并允许用户定义字段多项式,生成多项式和几个其他的参数。如新标准IEEE802.16-2004要求使用Reed-Solomon码及动态变化的模块大小。莱迪思的动态Reed-Solomon模块解码器核提供了一个理想的解决方案,以满足当今前向纠错领域的这种需求。这个核允许检查符号块的大小和数量通过输入端口而动态变化。该IP核可以与莱迪思的动态模块Reed-Solomon编码器一起使用,针对基于前向错误纠正应用的一个完整的Reed-Solomon码。

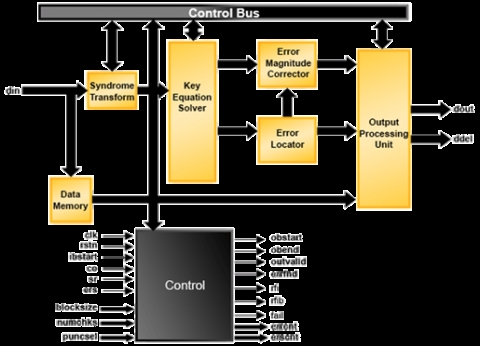

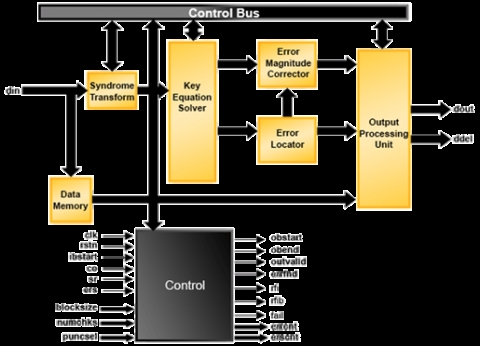

Reed-Solomon Reed-Solomon码的格式为RS(N,K),其中k是信息符号的数量,n是码字或块中符号的总数。码字中的每个符号是wsymb位宽。解调后在接收机中,Reed-Solomon解码器进行检测和编码数据的纠错。 然后,RS编码数据被处理,以确定是否在传输过程中发生任何错误。一旦确定了错误的数量,解码器决定是否他们处于校正范围内。确定后,解码器对接收到的数据进行纠错。下图说明了Reed-Solomon解码器的操作。

莱迪思的动态Reed-Solomon解码器 IP 符合几个行业标准,包括近期的IEEE 802.16-2004,可自定义配置,以支持其他非标准应用。该解码器支持很大范围的符号宽度,并允许用户定义字段多项式,生成多项式和几个其他的参数。如新标准IEEE802.16-2004要求使用Reed-Solomon码及动态变化的模块大小。莱迪思的动态Reed-Solomon模块解码器核提供了一个理想的解决方案,以满足当今前向纠错领域的这种需求。这个核允许检查符号块的大小和数量通过输入端口而动态变化。该IP核可以与莱迪思的动态模块Reed-Solomon编码器一起使用,针对基于前向错误纠正应用的一个完整的Reed-Solomon码。

Reed-Solomon Reed-Solomon码的格式为RS(N,K),其中k是信息符号的数量,n是码字或块中符号的总数。码字中的每个符号是wsymb位宽。解调后在接收机中,Reed-Solomon解码器进行检测和编码数据的纠错。 然后,RS编码数据被处理,以确定是否在传输过程中发生任何错误。一旦确定了错误的数量,解码器决定是否他们处于校正范围内。确定后,解码器对接收到的数据进行纠错。下图说明了Reed-Solomon解码器的操作。

查看 动态Reed-Solomon解码器 详细介绍:

- 查看 动态Reed-Solomon解码器 完整数据手册

- 联系 动态Reed-Solomon解码器 供应商

Block Diagram of the 动态Reed-Solomon解码器

FPGA IP

- RT-630-FPGA Hardware Root of Trust Security Processor for Cloud/AI/ML SoC FIPS-140

- Complete USB Type-C Power Delivery PHY, RTL, and Software

- Ethernet TSN Switch IP Core - Efficient and Massively Customizable

- CXL 2.0 Agilex FPGA Acclerator Card

- PCIe Gen3 to SRIO Gen3 Bridge (FPGA)

- 65nm/40nm Low Power eFPGA IP and Open Source FPGA Software