You are here:

DSP Extention Superscalar Processor

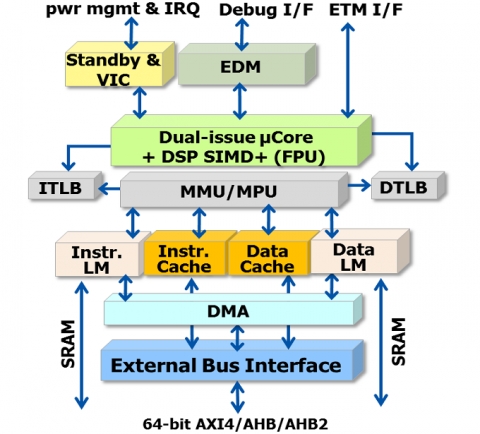

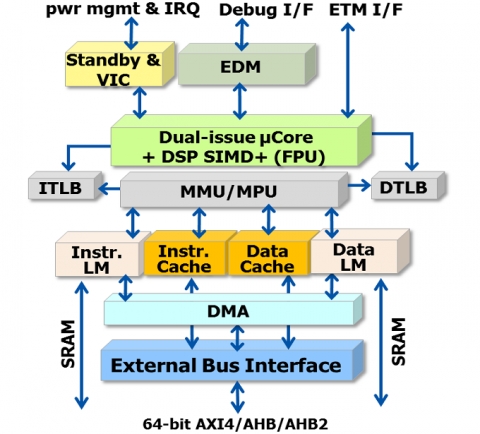

D15/D15F are the first dual-issue superscalar AndesCore™ processors. Both processors feature over 130 compiler friendly, general purpose DSP and SIMD instructions that enable easy DSP algorithm programming in C/C++. D15/D15F comes with a variety of configuration options, including MMU, cache and local memory. The 64-bit data buses for caches, local memory and the main bus provide the bandwidth needed for instruction fetch and data access. D15F includes a built-in IEEE-754 compliant floating point unit that enhances the floating point processing capability. D15/D15F is designed for diversified performance-driven applications on the embedded Linux, Real-Time OS or bare metal environment.

查看 DSP Extention Superscalar Processor 详细介绍:

- 查看 DSP Extention Superscalar Processor 完整数据手册

- 联系 DSP Extention Superscalar Processor 供应商

Block Diagram of the DSP Extention Superscalar Processor

Superscalar Processor IP

- Superscalar 32-bit Processor

- 32-bit 8-stage superscalar processor that supports RISC-V specification, including GCN

- 64-Bit 8-stage superscalar processor that supports RISC-V specification, including GCN

- 32-bit 8-stage superscalar processor that supports RISC-V specification, including GCNP (DSP)

- 32-bit 8-stage superscalar processor that supports RISC-V specification, including GCNP and Linux

- 64-bit 8-stage superscalar processor that supports RISC-V specification, including GCNP and Linux