You are here:

DSC Encoder

Display Stream Compression (DSC) standard was announced by Video Electronics Standards Association (VESA) in 2014 for video data compression and has been also adopted into the VESA's eDP v1.4 and the MIPI DSI standard.

Compliant with the VESA DSC 1.2a and 1.2b standards, CYBDSC2e

IP core supports various coding schemes (MMAP, BP, MPP, ICH) as well as color formats in YCbCr 4:4:4, 4:2:2, 4:2:0 and RGB. It transfers more pixel data over display links to save memory size in embedded frame buffers in display driver ICs and performs visually lossless compression, low gate count and latency for ultra-high definition display applications. It can be fastly and easily integrated into ASIC and FPGA applications for 4K / UHD TV, DisplayPort 1.4, USB Type-C device and AR / VR product.

CYB-DSC2e is available now for display designs with high performance but low risk and cost.

Compliant with the VESA DSC 1.2a and 1.2b standards, CYBDSC2e

IP core supports various coding schemes (MMAP, BP, MPP, ICH) as well as color formats in YCbCr 4:4:4, 4:2:2, 4:2:0 and RGB. It transfers more pixel data over display links to save memory size in embedded frame buffers in display driver ICs and performs visually lossless compression, low gate count and latency for ultra-high definition display applications. It can be fastly and easily integrated into ASIC and FPGA applications for 4K / UHD TV, DisplayPort 1.4, USB Type-C device and AR / VR product.

CYB-DSC2e is available now for display designs with high performance but low risk and cost.

查看 DSC Encoder 详细介绍:

- 查看 DSC Encoder 完整数据手册

- 联系 DSC Encoder 供应商

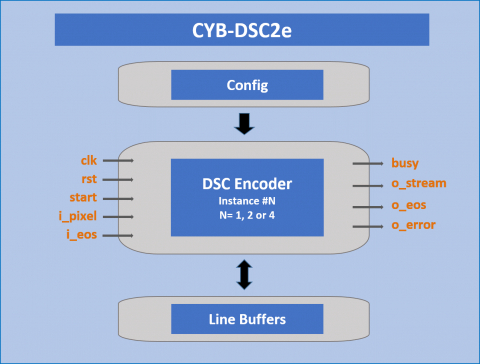

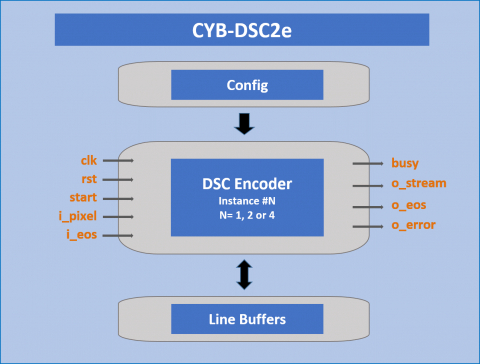

Block Diagram of the DSC Encoder

DSC IP

- VESA DSC (Display Stream Compression) 1.2b Video Encoder

- VESA DSC (Display Stream Compression) 1.2b Video Decoder

- ASIL-B Ready ISO 26262 Certified VESA DSC (Display Stream Compression) 1.1 Encoder

- VESA DisplayPort 1.4 RX IP Subsystem for Xilinx FPGAs

- VESA DSC 1.2b Encoder for Xilinx FPGAs

- VESA DSC 1.2b Decoder IP Core for Xilinx FPGAs