You are here:

DPDK-aware FPGA/GPP data mover

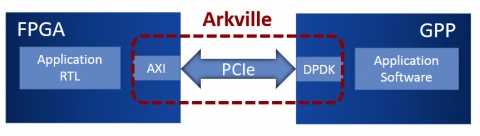

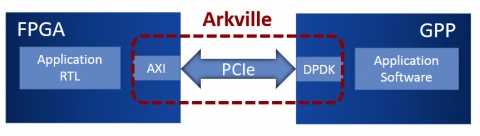

Arkville provides a high-throughput line-rate agnostic conduit between FPGA hardware and GPP software. Using industry-standard AXI interfaces on the FPGA side and DPDK interfaces on the software API/ABI side, Arkville provides an exceptional “out-of-the-box” solution for both hardware and software teams.

Because Arkville was designed with the specific goal of accelerating and empowering DPDK, the performance is significantly higher than one of a naïve DMA implementation on an FPGA.

Arkville has both a hardware and software component. The hardware component is an IP core that resides in the FPGA, producing and consuming AXI streams of packets making ingress or egress. The software component is a DPDK PMD “net/ark”, the Arkville DPDK poll-mode driver.

Together, an Arkville solution looks to software like a “vanilla” line rate agnostic FPGA-based NIC (without any specific MAC). DPDK applications do not need to change significantly in order to enjoy the advantages of FPGA hardware acceleration.

Because Arkville was designed with the specific goal of accelerating and empowering DPDK, the performance is significantly higher than one of a naïve DMA implementation on an FPGA.

Arkville has both a hardware and software component. The hardware component is an IP core that resides in the FPGA, producing and consuming AXI streams of packets making ingress or egress. The software component is a DPDK PMD “net/ark”, the Arkville DPDK poll-mode driver.

Together, an Arkville solution looks to software like a “vanilla” line rate agnostic FPGA-based NIC (without any specific MAC). DPDK applications do not need to change significantly in order to enjoy the advantages of FPGA hardware acceleration.

查看 DPDK-aware FPGA/GPP data mover 详细介绍:

- 查看 DPDK-aware FPGA/GPP data mover 完整数据手册

- 联系 DPDK-aware FPGA/GPP data mover 供应商

Block Diagram of the DPDK-aware FPGA/GPP data mover