MIPI D-PHY Universal IP - 4.5Gbps/lane, MIPI D-PHY v2.5 Compliant in TSMC 22ULP

You are here:

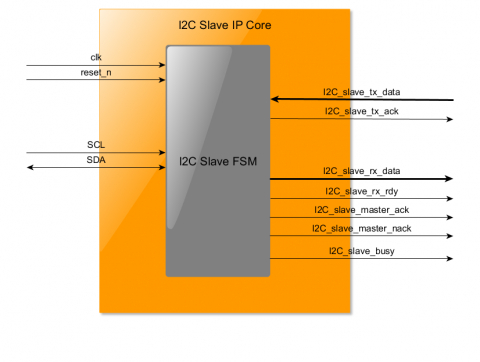

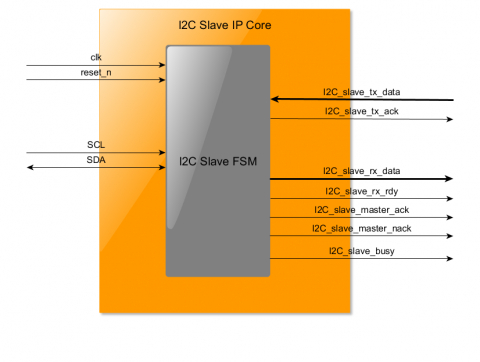

DO-254 I2C Slave

The I2C Slave IP Core implements an I2C Slave fully compliant to the I2C-bus specification and user manual Rev. 5 – 9 October 2012 for Standard-mode, Fast-mode and Fast-mode Plus (Fm+).

The Inter-Integrated Circuit (I2C) is a multi-master, multi-slave, single-ended, serial computer bus invented by Philips Semiconductor (now NXP Semiconductors). The I2C bus is typically used for attaching lower-speed peripheral ICs to processors and microcontrollers.

The I2C Master IP Core has been developed to DAL A according to the DO-254. For lower DAL levels reduced documentation sets are available. The core is also available as a netlist for DAL D or projects not needing the full RTL source.

Safe Core Devices provides two separate IP Cores, one for the I2C Slave IP Core and one for the I2C Master IP Core. If the system needs to be capable of transmitting and receiving both cores can be instantiated in the target device.

The Inter-Integrated Circuit (I2C) is a multi-master, multi-slave, single-ended, serial computer bus invented by Philips Semiconductor (now NXP Semiconductors). The I2C bus is typically used for attaching lower-speed peripheral ICs to processors and microcontrollers.

The I2C Master IP Core has been developed to DAL A according to the DO-254. For lower DAL levels reduced documentation sets are available. The core is also available as a netlist for DAL D or projects not needing the full RTL source.

Safe Core Devices provides two separate IP Cores, one for the I2C Slave IP Core and one for the I2C Master IP Core. If the system needs to be capable of transmitting and receiving both cores can be instantiated in the target device.

查看 DO-254 I2C Slave 详细介绍:

- 查看 DO-254 I2C Slave 完整数据手册

- 联系 DO-254 I2C Slave 供应商

Block Diagram of the DO-254 I2C Slave