You are here:

除法器

除法器IP核是一个单时钟周期除法器,每个时钟周期内完成一次整数除法。它支持有符号或无符号的输入,并提供可配置的输出延迟。

除法器IP核使用非还原除法算法实现整数的除法运算。

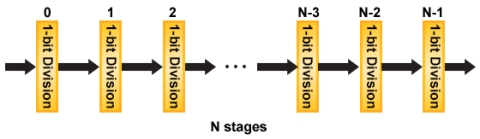

一个整数除法操作有N次1位除法,其中N是商的位数。

每一次除法产生1位商和部分余数。在最后一次除法,产生最后的商数和余数。1位除法使用一个加减器来比较部分余数和分母来得到一个新的部分余数。商的值取决于部分余数的符号。在最后一次除法,更正部分余数的值得到最终的余数。

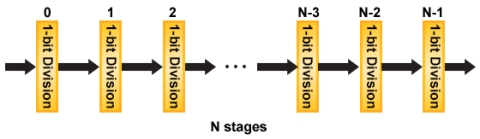

除法器IP核支持可配置的输出延迟。延迟可以是任意个时钟周期,从1到N。当延迟设置为M时,M次输出寄存器统一分配给N次1位除法运算。最后一次除法通常有输出寄存器。更多文本。

除法器IP核使用非还原除法算法实现整数的除法运算。

一个整数除法操作有N次1位除法,其中N是商的位数。

每一次除法产生1位商和部分余数。在最后一次除法,产生最后的商数和余数。1位除法使用一个加减器来比较部分余数和分母来得到一个新的部分余数。商的值取决于部分余数的符号。在最后一次除法,更正部分余数的值得到最终的余数。

除法器IP核支持可配置的输出延迟。延迟可以是任意个时钟周期,从1到N。当延迟设置为M时,M次输出寄存器统一分配给N次1位除法运算。最后一次除法通常有输出寄存器。更多文本。

查看 除法器 详细介绍:

- 查看 除法器 完整数据手册

- 联系 除法器 供应商

Block Diagram of the 除法器

FPGA IP

- RT-630-FPGA Hardware Root of Trust Security Processor for Cloud/AI/ML SoC FIPS-140

- Complete USB Type-C Power Delivery PHY, RTL, and Software

- Ethernet TSN Switch IP Core - Efficient and Massively Customizable

- CXL 2.0 Agilex FPGA Acclerator Card

- PCIe Gen3 to SRIO Gen3 Bridge (FPGA)

- 65nm/40nm Low Power eFPGA IP and Open Source FPGA Software