PCIe Gen 6 SERDES IP - supports up to 112G LR ethernet with low power and latency

You are here:

DiFi IP core

The DiFi IP core is a highly scalable and silicon agnostic implementation of the IEEE-ISTO Std 4900-2021: Digital IF Interoperability Standard v1.2.1 targeting ASIC, and FPGA technologies. The DiFi implementation builds on long-time experience designing IP cores for sending and receiving Radio IQ data over Ethernet networks, and delivers a flexible engine that is prepared for tight integration with software applications.

Source (Transmitter) and Sink (Receiver) components are provided, allowing for Duplex Equipment communication and supporting both Uplink and Downlink VITA-49 (VMEbus International Trade Association) stream directions.

DiFi IP from Chip Interfaces is designed to meet or exceed the requirements of stationary or mobile Satellite communication Ground Stations. The speed-optimized core can handle any solutions reaching from the “small footprint” to the most complex applications running on 100G Ethernet links.

Chip Interfaces DiFi IP comes with the widest parameter set available and has gone through extensive testing in our UVM regression test environment.

Source (Transmitter) and Sink (Receiver) components are provided, allowing for Duplex Equipment communication and supporting both Uplink and Downlink VITA-49 (VMEbus International Trade Association) stream directions.

DiFi IP from Chip Interfaces is designed to meet or exceed the requirements of stationary or mobile Satellite communication Ground Stations. The speed-optimized core can handle any solutions reaching from the “small footprint” to the most complex applications running on 100G Ethernet links.

Chip Interfaces DiFi IP comes with the widest parameter set available and has gone through extensive testing in our UVM regression test environment.

查看 DiFi IP core 详细介绍:

- 查看 DiFi IP core 完整数据手册

- 联系 DiFi IP core 供应商

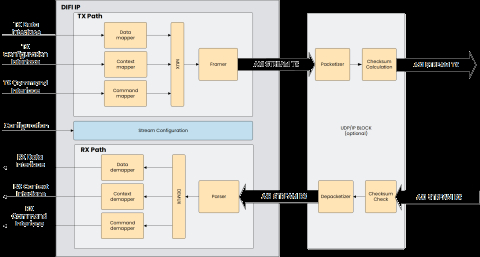

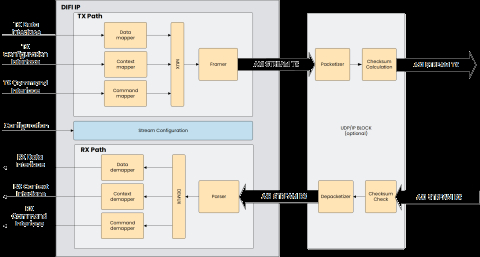

Block Diagram of the DiFi IP core