Secure-IC's Securyzr™ Tunable Hash (SHA3) Hardware accelerator

You are here:

Deep capture / high visibility Debug IP for Intel FPGA

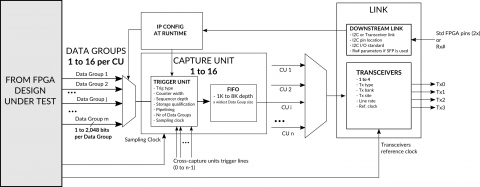

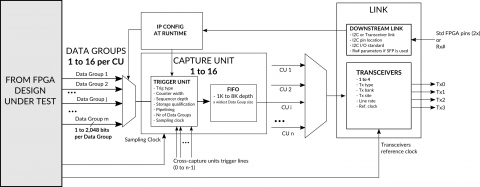

The customizable EXOSTIV IP core is a logic analyzer core that can be used to monitor the internal signals of an FPGA design without having to store the full trace data in the FPGA. The EXOSTIV IP core uses the FPGA transeivers as a high bandwidth channel to an external memory (in EXOSTIV Probe). The IP includes many advanced features for extending visibility on FPGA running at speed of operation- including data group definition and multiplexing, boolean trigger equations, data qualification (data filtering) and edge transition triggers. Because EXOSTIV IP core is synchronous to the design being monitored, all design clock constraints that are applied to your design are also applied to the components inside IP Core. EXOSTIV IP is at RTL level thanks to IP templates and constraints automatically generated at IP setup.

查看 Deep capture / high visibility Debug IP for Intel FPGA 详细介绍:

- 查看 Deep capture / high visibility Debug IP for Intel FPGA 完整数据手册

- 联系 Deep capture / high visibility Debug IP for Intel FPGA 供应商

Block Diagram of the Deep capture / high visibility Debug IP for Intel FPGA