You are here:

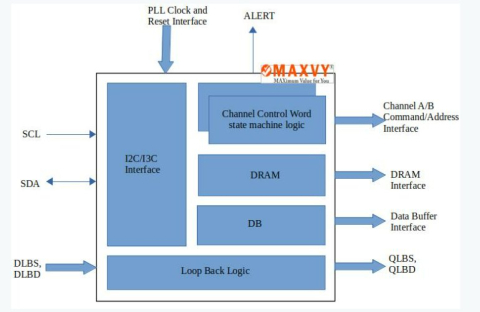

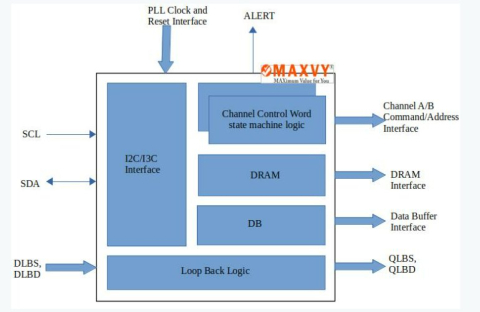

The DDR5RCD01 is a registering clock driver used on DDR5 RDIMMs and LRDIMMs. Its primary function is to buffer the Command/Address (CA) bus, chip selects, and clock between the host controller and the DRAMs. It also creates a BCOM bus which controls the

The DDR5RCD01 is a registering clock driver used on DDR5 RDIMMs and LRDIMMs. Its primary

function is to buffer the Command/Address (CA) bus, chip selects, and clock between the host

controller and the DRAMs. It also creates a BCOM bus which controls the data buffers for LRDIMMs.

function is to buffer the Command/Address (CA) bus, chip selects, and clock between the host

controller and the DRAMs. It also creates a BCOM bus which controls the data buffers for LRDIMMs.

查看 The DDR5RCD01 is a registering clock driver used on DDR5 RDIMMs and LRDIMMs. Its primary function is to buffer the Command/Address (CA) bus, chip selects, and clock between the host controller and the DRAMs. It also creates a BCOM bus which controls the 详细介绍:

- 查看 The DDR5RCD01 is a registering clock driver used on DDR5 RDIMMs and LRDIMMs. Its primary function is to buffer the Command/Address (CA) bus, chip selects, and clock between the host controller and the DRAMs. It also creates a BCOM bus which controls the 完整数据手册

- 联系 The DDR5RCD01 is a registering clock driver used on DDR5 RDIMMs and LRDIMMs. Its primary function is to buffer the Command/Address (CA) bus, chip selects, and clock between the host controller and the DRAMs. It also creates a BCOM bus which controls the 供应商

Block Diagram of the The DDR5RCD01 is a registering clock driver used on DDR5 RDIMMs and LRDIMMs. Its primary function is to buffer the Command/Address (CA) bus, chip selects, and clock between the host controller and the DRAMs. It also creates a BCOM bus which controls the

PMIC IP

- Power Management IC - I3C Basic Interface IP

- Input 3V-3.6V, VBG=1.23V BandGap; UMC 0.35um CDMOS Process

- 8V ~ 25V HV driver, UMC 0.35um 3.3V/5V/40V CDMOS logic process

- Power Management Unit(5-sets DC-DC, 2-sets REG, PowerSwitch, and Li-ion Charger) for Audio Platform; UMC 0.35um 3.3V/5V CDMOS process

- 110nm BCD process Synchronous High-Density Single-Port SRAM Compiler

- UMC 0.11um BCD process;Single-Port SRAM compiler