You are here:

针对低延迟优化的 DDR4 / DDR3/ DDR3L / LPDDR4 内存控制器 IP

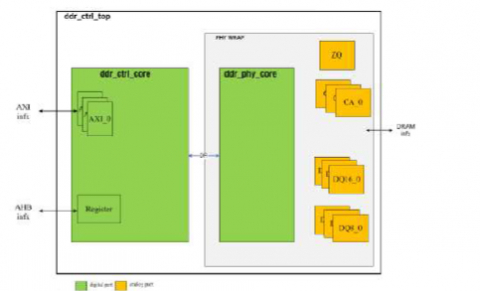

DDR(Double Data Rate)控制器 IP 适用于 LPDDR4 和 DDR4/3/3L,针对低latency进行了优化。控制器 IP silicon proven,并通过 DFI 4.0 接口连接到 DDR PHY,为客户提供完整的存储器接口解决方案,易于集成并加快上市时间。DDR IP 符合最新的 JEDEC 标准并且silicon proven。

此memory controller支持 DDR4、DDR3、DDR3L、LPDDR4 SDRAM。该memory controller是一个高速接口,用于内部engine和外部 SDRAM 总线之间的数据读/写,并传输内部信号以满足 SDRAM 规范。为了有更大的存储空间供 ASIC IC 存储,最好以低成本将存储器存储到外部 DRAM。所以需要DDR(Double Data Rate)控制器。ASIC IC 中的所有引擎都可以使用 AXI 接口通过 DDR 控制器将任何信息和数据存储到 DRAM。

对于写入:DDR 控制器将引擎的写入命令/地址和数据从 AXI 接口传输到 DRAM 接口,并将数据写入 DRAM。对于读取:DDR 控制器将引擎的读取命令/地址从 AXI 接口传输到 DRAM 接口。DRAM获得Read command/address后,DRAM会通过DRAM接口将数据转换到DDR控制器,然后DDR控制器通过AXI接口将数据传输到数据所有者引擎。

此memory controller支持 DDR4、DDR3、DDR3L、LPDDR4 SDRAM。该memory controller是一个高速接口,用于内部engine和外部 SDRAM 总线之间的数据读/写,并传输内部信号以满足 SDRAM 规范。为了有更大的存储空间供 ASIC IC 存储,最好以低成本将存储器存储到外部 DRAM。所以需要DDR(Double Data Rate)控制器。ASIC IC 中的所有引擎都可以使用 AXI 接口通过 DDR 控制器将任何信息和数据存储到 DRAM。

对于写入:DDR 控制器将引擎的写入命令/地址和数据从 AXI 接口传输到 DRAM 接口,并将数据写入 DRAM。对于读取:DDR 控制器将引擎的读取命令/地址从 AXI 接口传输到 DRAM 接口。DRAM获得Read command/address后,DRAM会通过DRAM接口将数据转换到DDR控制器,然后DDR控制器通过AXI接口将数据传输到数据所有者引擎。

查看 针对低延迟优化的 DDR4 / DDR3/ DDR3L / LPDDR4 内存控制器 IP 详细介绍:

- 查看 针对低延迟优化的 DDR4 / DDR3/ DDR3L / LPDDR4 内存控制器 IP 完整数据手册

- 联系 针对低延迟优化的 DDR4 / DDR3/ DDR3L / LPDDR4 内存控制器 IP 供应商