You are here:

DDR SDRAM控制器 - 非流水线技术

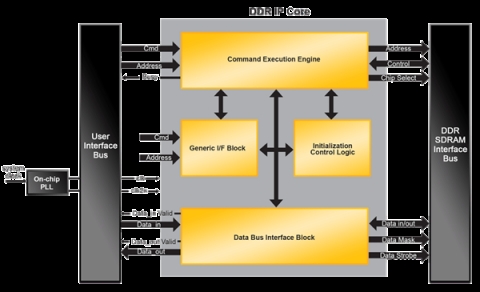

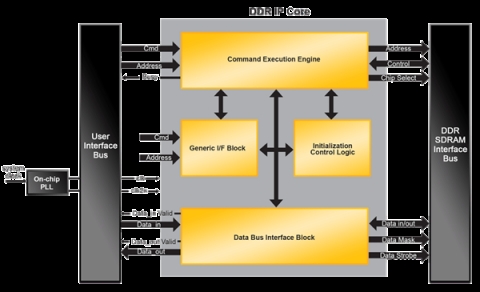

这个版本的莱迪思DDR SDRAM控制器不使用流水线,此IP核明显小于采用流水线的版本。DDR(双倍数据速率)SDRAM替代了SDRAM存储器,总线速率超过75MHz。DDR SDRAM在功能上与普通SDRAM类似,但通过在每个周期时钟信号的上下边沿都传输数据,使存储器带宽增加了一倍,实现了脉冲模式的数据传输。

DDR SDRAM控制器是一个参数可配置的核,让用户可以灵活地修改设计的数据宽度、突发传输速率和CAS延迟时间设置。此外,DDR核支持智能bank管理,通过维护一个''所有激活的bank"的数据库来实现。有了这个信息,DDR SDRAM控制器可以决定是否需要active或pre-charge指令。这将有效降低发送到DDR SDRAM读/写指令的延迟。

DDR SDRAM控制器是一个参数可配置的核,让用户可以灵活地修改设计的数据宽度、突发传输速率和CAS延迟时间设置。此外,DDR核支持智能bank管理,通过维护一个''所有激活的bank"的数据库来实现。有了这个信息,DDR SDRAM控制器可以决定是否需要active或pre-charge指令。这将有效降低发送到DDR SDRAM读/写指令的延迟。

查看 DDR SDRAM控制器 - 非流水线技术 详细介绍:

- 查看 DDR SDRAM控制器 - 非流水线技术 完整数据手册

- 联系 DDR SDRAM控制器 - 非流水线技术 供应商

Block Diagram of the DDR SDRAM控制器 - 非流水线技术

FPGA IP

- RT-630-FPGA Hardware Root of Trust Security Processor for Cloud/AI/ML SoC FIPS-140

- Complete USB Type-C Power Delivery PHY, RTL, and Software

- Ethernet TSN Switch IP Core - Efficient and Massively Customizable

- CXL 2.0 Agilex FPGA Acclerator Card

- PCIe Gen3 to SRIO Gen3 Bridge (FPGA)

- 65nm/40nm Low Power eFPGA IP and Open Source FPGA Software