You are here:

CSI2 TX; Camera Serial Interface, MIPI Compliant

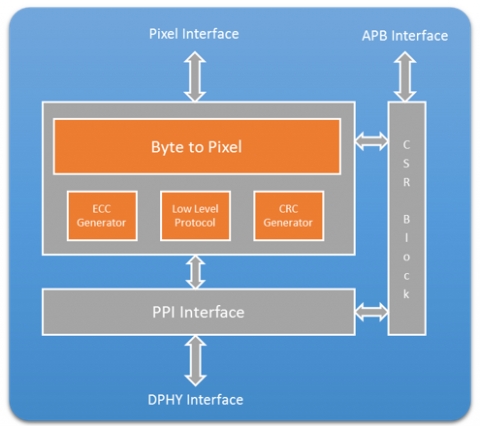

CSI2 – TX is part of HCL’s MIPI® compliant offerings. The CSI2 Transmitter IP supports Pixel Interface on the camera sensor side and the DPHY is supported through the PPF interface. The IP is designed to be operate as single or multiple data lanes (up to 4) based on the sensor bandwidth required in the camera module. It offers APB Bus interface by default for communication with MPU. It can be customized quickly if needed, for other leading industry standard bus interface to MPU such as Avalon, AXI4 – Lite and AHB.

This IP is efficient and functionally verified and well tested design for the Camera Serial Interface – 2 (CSI – 2 version 1.1) and D – PHY version 1.1 and can be immediately used in SoC designs in need of the CSI Interface.

This IP is efficient and functionally verified and well tested design for the Camera Serial Interface – 2 (CSI – 2 version 1.1) and D – PHY version 1.1 and can be immediately used in SoC designs in need of the CSI Interface.

查看 CSI2 TX; Camera Serial Interface, MIPI Compliant 详细介绍:

- 查看 CSI2 TX; Camera Serial Interface, MIPI Compliant 完整数据手册

- 联系 CSI2 TX; Camera Serial Interface, MIPI Compliant 供应商

Block Diagram of the CSI2 TX; Camera Serial Interface, MIPI Compliant

CSI2 IP

- MIPI CSI-2 Controller Core V2

- MIPI CSI-2 controller Receiver v 2.1, Compatible with MIPI C-PHY v1.2 & DPHY v2.1.

- MIPI C-PHY/D-PHY Combo CSI-2 RX+ IP (6.0Gsps/trio, 4.5Gbps/lane) in TSMC N6

- MIPI CSI DSI Controller - CPHY CSI-2 Transmitter v 2.1, Compatible with MIPI C-PHY v1.2 & DPHY v2.1.

- MIPI C-PHY/D-PHY Combo CSI-2 TX+ IP in TSMC 40ULP

- MIPI C-PHY/D-PHY Combo CSI-2 TX 4.5Gsps/trio in TSMC 28nm