You are here:

Cross-Correlator With 64x2 Channels

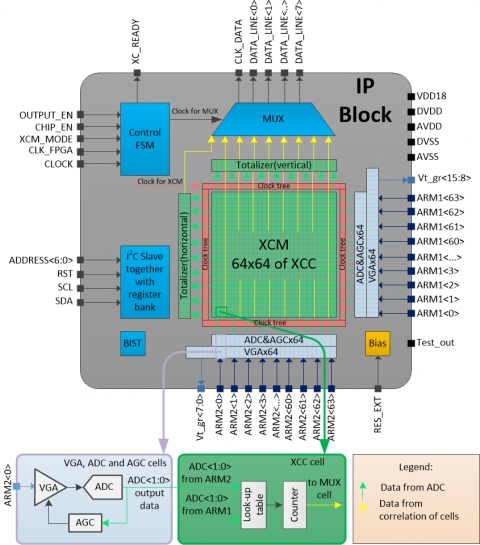

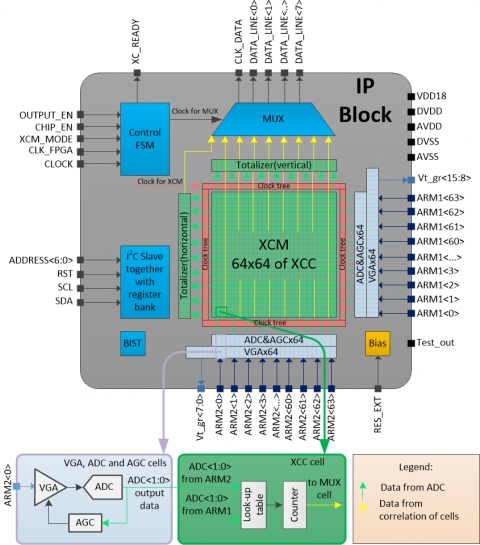

PMCC_XCM_64x64 is an IP block capable of calculating the cross-correlations between 64x2 analog signals supplied to the inputs ARM1<63:0> and ARM2<63:0>. The IP block operates sequentially in two modes: integration and data readout. During the integration mode, the IP block calculates cross-correlation between the signals for a preset period of time. During the data readout mode, the IP block prepares the data and transmits it to the 8-bit output multiplexer.

Analog signals from inputs ARM1 and ARM2 with the bandwidth from 10 MHz to 500 MHz are passed through the variable gain amplifiers (VGAs) to the 2-bit A/D converters. An automatic gain control (AGC) circuit is using the 2-bit data to adjust the input signal level at the ADC’s input through adjusting the VGA’s gain. The AGC loop controls the VGA gain in such a manner that the average duty cycle of the ADC’s LSB would be equal to 0.7 by default.

The data from the ADC block is passed to the main functional block of the cross-correlator IP – the Cross- Correlation Matrix. This block is responsible for crosscorrelation of 64 2-bit signals from one arm with 64 2-bit signals from another arm. The matrix consists of 4096 crosscorrelation cells, 64 vertical totalizers and 64 horizontal totalizers. The cross-correlation cell (XCC) consists of the multiplication and accumulation blocks. The power consumption of a single correlation cell is minimized to ensure high power efficiency of the IP block.

A Totalizer consists of an array of adder cells which count the number of occurrences of each possible two-bit input values supplied from the A/D converter.

An Output Multiplexer (MUX) performs serializing of the data stored in Cross-Correlation Cells and Totalizer Cells. The I2C Interface is built in for the IP block’s control.

Analog signals from inputs ARM1 and ARM2 with the bandwidth from 10 MHz to 500 MHz are passed through the variable gain amplifiers (VGAs) to the 2-bit A/D converters. An automatic gain control (AGC) circuit is using the 2-bit data to adjust the input signal level at the ADC’s input through adjusting the VGA’s gain. The AGC loop controls the VGA gain in such a manner that the average duty cycle of the ADC’s LSB would be equal to 0.7 by default.

The data from the ADC block is passed to the main functional block of the cross-correlator IP – the Cross- Correlation Matrix. This block is responsible for crosscorrelation of 64 2-bit signals from one arm with 64 2-bit signals from another arm. The matrix consists of 4096 crosscorrelation cells, 64 vertical totalizers and 64 horizontal totalizers. The cross-correlation cell (XCC) consists of the multiplication and accumulation blocks. The power consumption of a single correlation cell is minimized to ensure high power efficiency of the IP block.

A Totalizer consists of an array of adder cells which count the number of occurrences of each possible two-bit input values supplied from the A/D converter.

An Output Multiplexer (MUX) performs serializing of the data stored in Cross-Correlation Cells and Totalizer Cells. The I2C Interface is built in for the IP block’s control.

查看 Cross-Correlator With 64x2 Channels 详细介绍:

- 查看 Cross-Correlator With 64x2 Channels 完整数据手册

- 联系 Cross-Correlator With 64x2 Channels 供应商

Block Diagram of the Cross-Correlator With 64x2 Channels