MIPI C-PHY v1.0 D-PHY v1.2 RX 2 trios/2 Lanes in TSMC (12nm, N5)

You are here:

波峰因数减少(Crest Factor Reduction)IP

波峰因子减少(CFR)选择性地降低宽带数字信号的峰均比(PAR),用于例如3G码分多址(CDMA)或长期演进(LTE)无线应用。

莱迪思的峰值对消波峰因子减少(PC-CFR)IP核包含在专为HetNet应用而优化的 数字前端(DFE)IP套件中。该IP核高度可编程并且可以进行定制,以达到所需的资源与性能比。IP核专为用于ECP3 FPGA系列而优化,实现了LTE信号的PAR值降低多达4dB。

欲了解更多有关CFR IP的信息,请点击下面的“START HERE”按钮。

莱迪思的峰值对消波峰因子减少(PC-CFR)IP核包含在专为HetNet应用而优化的 数字前端(DFE)IP套件中。该IP核高度可编程并且可以进行定制,以达到所需的资源与性能比。IP核专为用于ECP3 FPGA系列而优化,实现了LTE信号的PAR值降低多达4dB。

欲了解更多有关CFR IP的信息,请点击下面的“START HERE”按钮。

查看 波峰因数减少(Crest Factor Reduction)IP 详细介绍:

- 查看 波峰因数减少(Crest Factor Reduction)IP 完整数据手册

- 联系 波峰因数减少(Crest Factor Reduction)IP 供应商

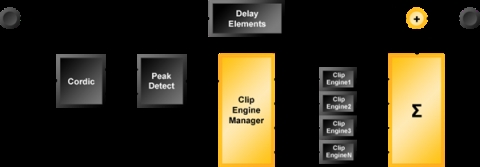

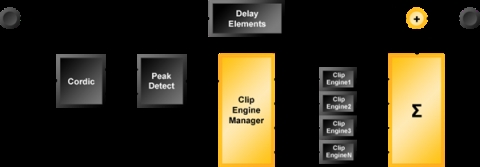

Block Diagram of the 波峰因数减少(Crest Factor Reduction)IP

FPGA IP

- RT-630-FPGA Hardware Root of Trust Security Processor for Cloud/AI/ML SoC FIPS-140

- Complete USB Type-C Power Delivery PHY, RTL, and Software

- Ethernet TSN Switch IP Core - Efficient and Massively Customizable

- CXL 2.0 Agilex FPGA Acclerator Card

- PCIe Gen3 to SRIO Gen3 Bridge (FPGA)

- 65nm/40nm Low Power eFPGA IP and Open Source FPGA Software