支持CXL.io,CXL.cache,CXL.mem 的 Compute Express Link(CXL)规范的控制器IP

查看 支持CXL.io,CXL.cache,CXL.mem 的 Compute Express Link(CXL)规范的控制器IP 详细介绍:

- 查看 支持CXL.io,CXL.cache,CXL.mem 的 Compute Express Link(CXL)规范的控制器IP 完整数据手册

- 联系 支持CXL.io,CXL.cache,CXL.mem 的 Compute Express Link(CXL)规范的控制器IP 供应商

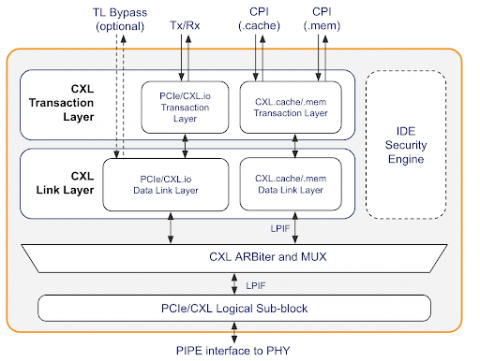

Block Diagram of the 支持CXL.io,CXL.cache,CXL.mem 的 Compute Express Link(CXL)规范的控制器IP

Video Demo of the 支持CXL.io,CXL.cache,CXL.mem 的 Compute Express Link(CXL)规范的控制器IP

In this video, we demonstrate the Rambus Controller IP for CXL 2.0 and the CXL.mem protocol used to access Host-managed Device Memory, or HDM. This demonstration is performed using Intel’s Pre-Production Xeon processor as a host, connected to an FPGA board, instantiating Rambus' CXL Controller and CXL.mem test design.