Process Detector (For DVFS and monitoring process variation)

具有 FIFO、软件和硬件流量控制的可配置 UART

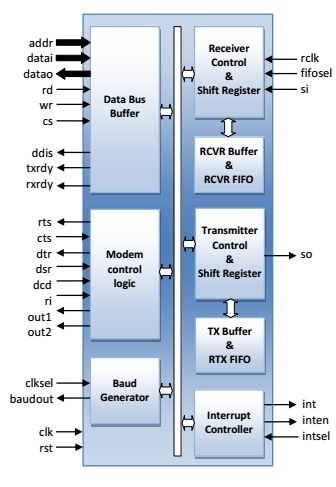

D16950的交付件集成了可编程的比特率发生器,支持时序参考时钟输入按照1到(216-1)的除数分频,并产生n×时钟用于驱动内部发射机逻辑,还可以使用此n×时钟驱动接收机逻辑。此外,这个IP还集成了完整的调制解调器控制功能和处理器中断系统。可以根据客户的要求编程中断,从而减少处理通信链路所需的计算。D16950核心包括所有(16450、16550、16650和16750)功能和附加功能。D16950具有ICR寄存器,提供了UART工作配置的附加功能。数据传输可以通过连接到RI(用于收发器)或DSR(仅用于接收器)引脚的外部时钟来同步。NMR寄存器允许启用带或不带特殊字符的9位模式传输。可以通过触发电平寄存器来控制对FIFO的写入和读取。触发电平寄存器可以设置从1到127的任何值。

在FIFO模式下,有选择的自动流控制功能,可以显著减少软件负载,并通过控制RTS输出和CTS输入信号来自动提高系统效率,通过控制串行数据流。

该核心非常适用于UART核心和微控制器由相同的时钟信号驱动并在同一ASIC或FPGA芯片内实现的应用程序。然而,它也是用于独立实现的专有解决方案,其中需要在单个芯片内实现多个UART并由一些外部芯片驱动。由于具有通用接口,D16950核心的实现和验证非常简单,只需在完整系统中消除一些时钟树即可。与我们的所有UART核心一样,D16950包含了完全自动化的测试台和完整的测试集,可以在SoC设计流程的每个阶段轻松进行包验证。这种高效的解决方案是一种技术无关的设计,可以在各种工艺技术上实现。

查看 具有 FIFO、软件和硬件流量控制的可配置 UART 详细介绍:

- 查看 具有 FIFO、软件和硬件流量控制的可配置 UART 完整数据手册

- 联系 具有 FIFO、软件和硬件流量控制的可配置 UART 供应商

Block Diagram of the 具有 FIFO、软件和硬件流量控制的可配置 UART