MIPI C-PHY v2.0 D-PHY v2.1 RX 2 trios/2 Lanes in TSMC (N5, N3E, N3P)

You are here:

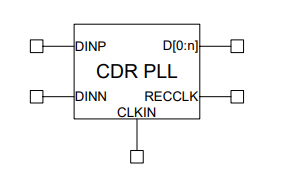

Clock/Data Recovery PLL

The MXL-PLL-CDR is a clock/data recovery PLL implemented using a digital CMOS process. It is highly integrated and require no external components. Differential circuit techniques are employed to attain low jitter in the noisy environment typical of multi-million gates digital chip.

The circuit is designed in a modular fashion and desensitized to process variations. This facilitates process migration, and results in a robust design.

The circuit is designed in a modular fashion and desensitized to process variations. This facilitates process migration, and results in a robust design.

查看 Clock/Data Recovery PLL 详细介绍:

- 查看 Clock/Data Recovery PLL 完整数据手册

- 联系 Clock/Data Recovery PLL 供应商

Block Diagram of the Clock/Data Recovery PLL

CDR IP

- SONET/SDH OC-3 / OC-12 Transceiver/CDR PHY

- Dual Band 25.78125G/28Gbps SerDes/CDR Available in TSMC 28nm 9LM HPC+

- Low jitter, low-power clock-deskew PLL operating from 6GHz to 9.5GHz

- 2.5 Gbps Transceiver core

- 4.25 Gbps Quad Multistandard SerDes

- Deserializer 1:32 for 8.5-11.3Gb/s for SONET/SDH, 10Ge, XFI, Back Plain