You are here:

CAN 2.0 Controller with DMA

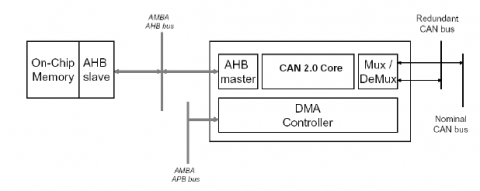

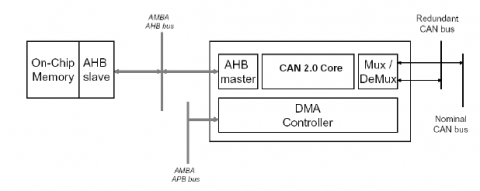

The GRCAN core is a CAN controller with an AHB DMA backend. The APB bus is used for configuration, control and status handling and the AHB bus is used for retrieving and storing CAN messages in memory external to the CAN controller. GRCAN supports transmission and reception of sets of messages by use of circular buffers located in memory external to the core. Separate transmit and receive buffers are assumed. Reception and transmission of sets of messages can be ongoing simultaneously.

查看 CAN 2.0 Controller with DMA 详细介绍:

- 查看 CAN 2.0 Controller with DMA 完整数据手册

- 联系 CAN 2.0 Controller with DMA 供应商

Block Diagram of the CAN 2.0 Controller with DMA

CAN 2.0 Controller with DMA IP

- Compute Express Link (CXL) 2.0 Controller with AMBA AXI interface

- Universal NVM Express Controller (UNEX)

- USB 2.0 OTG High / Full / Low- Speed Dual Role IP Core

- PCIe 2.1 Controller supporting Root Port, Endpoint, Dual-mode Configurations, with Built-in DMA and Configurable AMBA AXI Interconnect

- CXL 2.0 Dual Mode Controller

- Direct Memory Access Controller IP Core