You are here:

Camera Link IP Core

The Camera Link IP Core is designed for building vision systems incorporating Camera Link™ communication interfaces including Base, Medium & Full Channel Link configurations. The core supports camera control signals, serial communication, and video data. It is designed for building both Camera and Frame Grabber devices.

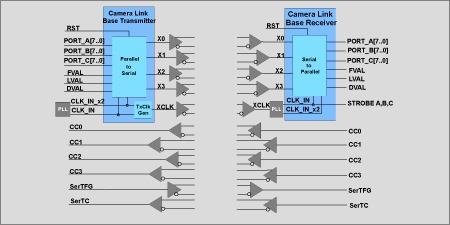

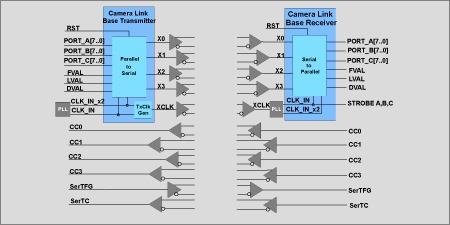

The Camera Link standard is based on Channel Link® technology developed by National Semiconductor. Channel Link uses LVDS technology for transmitting digital data using a parallel-to-serial transmitter and a serial-to parallel-receiver to transmit data at rates up to 2.38 Gbps. The base Channel Link standard uses 28 bits to represent up to 24 bits of pixel data and 3 bits for Video Sync signals. These consist of Data Valid, Frame Valid, and Line Valid bits. The data is serialized 7:1, and the four data streams and a dedicated clock are driven over five LVDS pairs. The Receiver accepts the four LVDS data streams and one LVDS clock, and then deserializes the data into 28 bits of parallel data and a clock.

The core is designed for Altera® field programmable logic devices and is supplied with an easy-to-use Quartus® SOPC Builder Ready component.

The Camera Link standard is based on Channel Link® technology developed by National Semiconductor. Channel Link uses LVDS technology for transmitting digital data using a parallel-to-serial transmitter and a serial-to parallel-receiver to transmit data at rates up to 2.38 Gbps. The base Channel Link standard uses 28 bits to represent up to 24 bits of pixel data and 3 bits for Video Sync signals. These consist of Data Valid, Frame Valid, and Line Valid bits. The data is serialized 7:1, and the four data streams and a dedicated clock are driven over five LVDS pairs. The Receiver accepts the four LVDS data streams and one LVDS clock, and then deserializes the data into 28 bits of parallel data and a clock.

The core is designed for Altera® field programmable logic devices and is supplied with an easy-to-use Quartus® SOPC Builder Ready component.

查看 Camera Link Transceiver 详细介绍:

- 查看 Camera Link Transceiver 完整数据手册

- 联系 Camera Link Transceiver 供应商

Block Diagram of the Camera Link Transceiver