You are here:

Bit Block Transfer (BitBLT) Graphics Engine IP Core

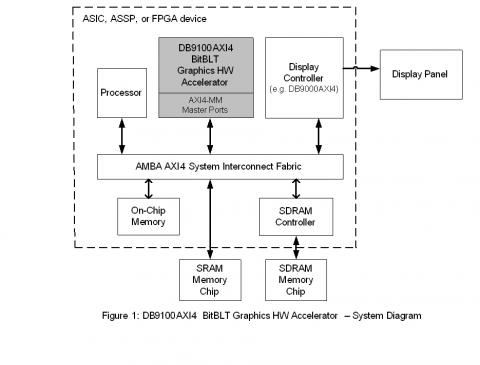

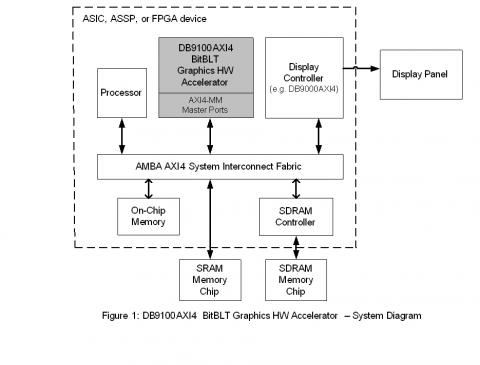

The Bit Block Transfer (BitBLT) Graphics Engine IP Core provides hardware acceleration of block moves with Raster Operation (256 data manipulation operations) of off-screen or on-screen data within frame buffer memory in a graphic display system. In addition, the DB9100AXI4 provides hardware accelerated 2D graphics rendering capability. Utilizing the accelerated BitBLT & 2 D graphics operations, the DB9100AXI4 IP Core greatly increases software productivity.

The Bit Block Transfer (BitBLT) Graphics Engine IP Core works in parallel with the TFT LCD Controller IP Core, interfacing a microprocessor and frame buffer memory via the AMBA AXI4 Bus to a TFT LCD panel. Frame buffer memory typically is either on-chip SRAM memory or larger off-chip SRAM or SDRAM.

The Bit Block Transfer (BitBLT) Graphics Engine IP Core works in parallel with the TFT LCD Controller IP Core, interfacing a microprocessor and frame buffer memory via the AMBA AXI4 Bus to a TFT LCD panel. Frame buffer memory typically is either on-chip SRAM memory or larger off-chip SRAM or SDRAM.

查看 BitBLT Graphics Hardware Accelerator (AXI4 Bus) 详细介绍:

- 查看 BitBLT Graphics Hardware Accelerator (AXI4 Bus) 完整数据手册

- 联系 BitBLT Graphics Hardware Accelerator (AXI4 Bus) 供应商

Block Diagram of the BitBLT Graphics Hardware Accelerator (AXI4 Bus)