You are here:

BitBLT Graphics Hardware Accelerator (AHB Bus)

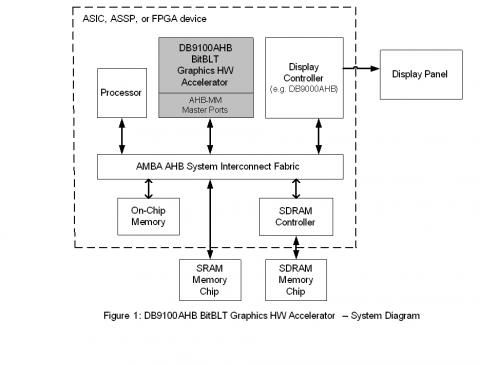

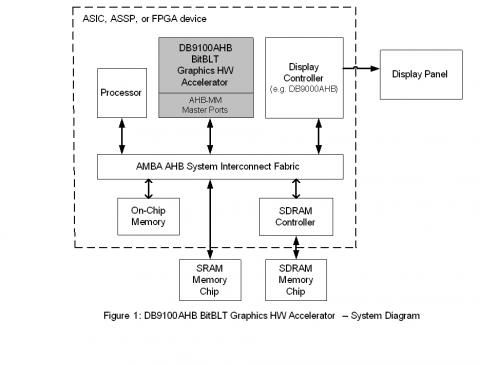

The Digital Blocks DB9100AHB BitBLT Graphics Hardware Accelerator Verilog IP Core renders a graphics frame by generating new bitmaps from commands to combining existing bitmaps on and off-screen using one of 256 Raster Operations. A Raster Operation (ROP) is a bitwise Boolean operation (such as AND, OR, XOR, NOT).

The DB9100AHB also contains a Monochrome Bitmap Color Expansion feature, typically used for font expansion of compressed character bitmaps. A 1-bit depth bitmap is expanded to one of two colors, a foreground or background color, with the foreground color representing the text, and the background color the non-text background.

The DB9100AHB also contains a programmable Alpha Blend unit, blending two bitmaps into one.

The DB9100AHB interfaces to a microprocessor and frame buffer memory via the AMBA AHB Interconnect, providing high performance memory throughput. The DB9100AHB contains a DMA Command Linked-List Processing Unit, for independently reading and processing graphics commands from the host processor.

The DB9100AHB also contains a Monochrome Bitmap Color Expansion feature, typically used for font expansion of compressed character bitmaps. A 1-bit depth bitmap is expanded to one of two colors, a foreground or background color, with the foreground color representing the text, and the background color the non-text background.

The DB9100AHB also contains a programmable Alpha Blend unit, blending two bitmaps into one.

The DB9100AHB interfaces to a microprocessor and frame buffer memory via the AMBA AHB Interconnect, providing high performance memory throughput. The DB9100AHB contains a DMA Command Linked-List Processing Unit, for independently reading and processing graphics commands from the host processor.

查看 BitBLT Graphics Hardware Accelerator (AHB Bus) 详细介绍:

- 查看 BitBLT Graphics Hardware Accelerator (AHB Bus) 完整数据手册

- 联系 BitBLT Graphics Hardware Accelerator (AHB Bus) 供应商

Block Diagram of the BitBLT Graphics Hardware Accelerator (AHB Bus)