You are here:

BCH Error Correcting Code ECC

BCH code statistics for different `$mm` `$tt`

Zero latency, low gate count, low power, asynchronous BCH Code based Error Correction FEC:

The whole operation of encoding and decoding is asynchronous and is pure combinatorial gates without use of any synchronous logic, making it zero latency RTL.

Symbol Size is 1 bit and variables are ‘m’ bits wide for Galois Field operations.

Zero latency, low gate count, low power, asynchronous BCH Code based Error Correction FEC:

The whole operation of encoding and decoding is asynchronous and is pure combinatorial gates without use of any synchronous logic, making it zero latency RTL.

Symbol Size is 1 bit and variables are ‘m’ bits wide for Galois Field operations.

查看 BCH Error Correcting Code ECC 详细介绍:

- 查看 BCH Error Correcting Code ECC 完整数据手册

- 联系 BCH Error Correcting Code ECC 供应商

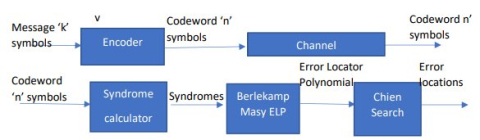

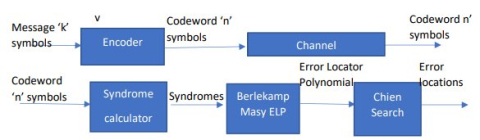

Block Diagram of the BCH Error Correcting Code ECC