You are here:

AXI4 Memory-Mapped to/from AXI4-Stream DMA

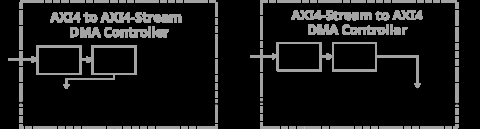

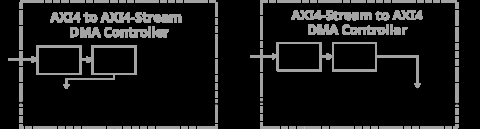

The AXI4-DMA IP core interfaces AXI4 data bus to provide data transfers from AXI4 Memory-Mapped port to AXI4-Stream port or the other way round thus serving as a Direct Memory Access controller.

The core is supplied as independent Memory-Mapped to Stream and Stream to Memory-Mapped single DMA channel modules each with its own AXI4-LITE slave. The modules operate in direct register mode, where control and status registers (CSR) are used to configure descriptors and trigger transfers from the host system. Data bus width, address width, burst length and other parameters are customizable at synthesis time, allowing flexible resource management and adjusment for diverse peripherals. Stream master and slave logic includes convenient data width converters supporting byte alligned 8, 16, 24, 32 and higher bit widths.

The EDI-AXI4-DMA core is provided as VHDL source or packaged for the Xilinx IP Integrator tool and can be combined with other Xilinx IP cores. The parameters are completely configurable in the package allowing the designer to adjust for different peripherals.

The core is supplied as independent Memory-Mapped to Stream and Stream to Memory-Mapped single DMA channel modules each with its own AXI4-LITE slave. The modules operate in direct register mode, where control and status registers (CSR) are used to configure descriptors and trigger transfers from the host system. Data bus width, address width, burst length and other parameters are customizable at synthesis time, allowing flexible resource management and adjusment for diverse peripherals. Stream master and slave logic includes convenient data width converters supporting byte alligned 8, 16, 24, 32 and higher bit widths.

The EDI-AXI4-DMA core is provided as VHDL source or packaged for the Xilinx IP Integrator tool and can be combined with other Xilinx IP cores. The parameters are completely configurable in the package allowing the designer to adjust for different peripherals.

查看 AXI4 Memory-Mapped to/from AXI4-Stream DMA 详细介绍:

- 查看 AXI4 Memory-Mapped to/from AXI4-Stream DMA 完整数据手册

- 联系 AXI4 Memory-Mapped to/from AXI4-Stream DMA 供应商

Block Diagram of the AXI4 Memory-Mapped to/from AXI4-Stream DMA

AXI4 IP

- PCIe 4.0 Controller with AMBA AXI interface

- Display Controller - LCD / OLED Panels (AXI4 Bus)

- DMA AXI4-Stream to/from AXI4 Memory Map - Scatter-Gather Descriptor List

- DMA AXI4-Stream to/from AXI4 Memory Map - Scatter-Gather Command Stream List

- VME System Controller with AXI4 compliant user interface

- VME System Controller with AXI4 user interface and 2eSST support