Secure-IC's Securyzr™ Fully Digital Physically Unclonable Function (PUF) - PQC Ready

You are here:

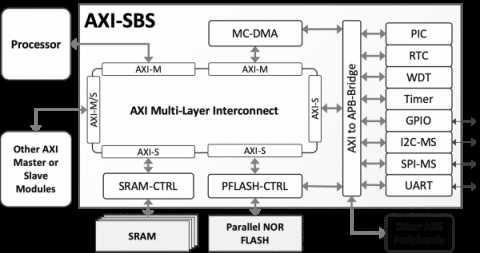

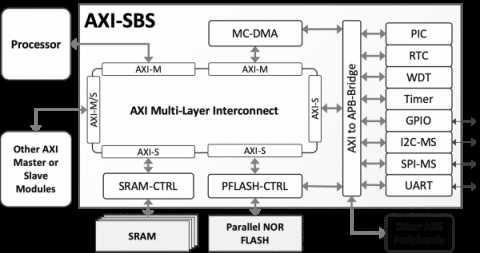

AXI Subsystem

The AXI-SBS is an integrated, verified, AMBA® compliant hardware/software system ready for embedded applications using processors with AXI4 interfaces such as the BA20, BA21, and several RISC-V Implementations.

The AXI Subsystem combines peripheral and interface IP cores with drivers and other essential software and an AXI/APB bus infra- structure. It is designed to work well with the user's choice of processor, and has been specifically tested with those from CAST.

The AXI-SBS integrates a 32-bit multilayer AXI fabric with an SRAM controller, a multi-channel DMA controller, an external memory controller, suitable for accessing off-chip parallel NOR-flash devices or SRAMs, an APB bridge, and a set of APB peripherals, such as timers and serial interfaces.

The AXI-SBS was designed with industry best practices, and its reliability and low risk have been proven through both rigorous verification and customer production. It is delivered in human-readable Verilog source code along with comprehensive documentation for each module, example drivers, and software exercising all the peripherals.

This subsystem can be mapped to any Intel, Lattice, MicroSemi, or Xilinx programmable device, or to any ASIC technology, provided sufficient silicon resources are available. Please contact CAST Sales to get accurate characterization data for your specific implementation requirements.

The AXI Subsystem combines peripheral and interface IP cores with drivers and other essential software and an AXI/APB bus infra- structure. It is designed to work well with the user's choice of processor, and has been specifically tested with those from CAST.

The AXI-SBS integrates a 32-bit multilayer AXI fabric with an SRAM controller, a multi-channel DMA controller, an external memory controller, suitable for accessing off-chip parallel NOR-flash devices or SRAMs, an APB bridge, and a set of APB peripherals, such as timers and serial interfaces.

The AXI-SBS was designed with industry best practices, and its reliability and low risk have been proven through both rigorous verification and customer production. It is delivered in human-readable Verilog source code along with comprehensive documentation for each module, example drivers, and software exercising all the peripherals.

This subsystem can be mapped to any Intel, Lattice, MicroSemi, or Xilinx programmable device, or to any ASIC technology, provided sufficient silicon resources are available. Please contact CAST Sales to get accurate characterization data for your specific implementation requirements.

查看 AXI Subsystem 详细介绍:

- 查看 AXI Subsystem 完整数据手册

- 联系 AXI Subsystem 供应商

Block Diagram of the AXI Subsystem