You are here:

AMBA AHB 4 Channel DMA Controller (70119)

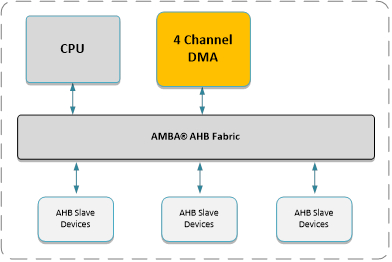

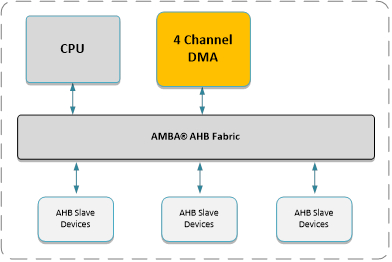

The DMA is a multiple-channel direct memory access controller. The DMA IP Core is a Verilog HDL design that can be used in ASIC, Structured ASIC and FPGA designs. The design is intended to be used with AMBA based systems as a controller to transfer data directly from system memory to memory or system memory to peripheral device or IP Core.

Once configured and enabled, the DMA controller is primarily an AHB Master, which initiates data transfers across the AHB bus to/from a peripheral device through the DMA Buffer. The DMA Buffer is a 16x32-bit FIFO, which is useful for peripheral devices requiring a steady stream of data such as an LCD Controller, Ethernet MAC or other communication device.

The DMA controller contains useful features such as incrementing and non-incrementing addressing and link list operation. Linked list support is useful for non-contiguous memory transfer operations.

The DMA Channel Arbiter determines which DMA Channel has access to the external AHB Master Bus. A round-robin algorithm is implemented in which each active channel has equal priority.

Once configured and enabled, the DMA controller is primarily an AHB Master, which initiates data transfers across the AHB bus to/from a peripheral device through the DMA Buffer. The DMA Buffer is a 16x32-bit FIFO, which is useful for peripheral devices requiring a steady stream of data such as an LCD Controller, Ethernet MAC or other communication device.

The DMA controller contains useful features such as incrementing and non-incrementing addressing and link list operation. Linked list support is useful for non-contiguous memory transfer operations.

The DMA Channel Arbiter determines which DMA Channel has access to the external AHB Master Bus. A round-robin algorithm is implemented in which each active channel has equal priority.

查看 AMBA AHB 4 Channel DMA Controller (70119) 详细介绍:

- 查看 AMBA AHB 4 Channel DMA Controller (70119) 完整数据手册

- 联系 AMBA AHB 4 Channel DMA Controller (70119) 供应商

Block Diagram of the AMBA AHB 4 Channel DMA Controller (70119)