You are here:

All Digital PLL

The All Digital is an all digital implementation of a phase locked loop. PLLs are widely used in telecom applications for clock recovery, clock generation and clock supervision.

Different phase dtectors (FIFO fill level, phase erros, and so on) may be used and can be adapted to perfectely fit the application.

Different phase dtectors (FIFO fill level, phase erros, and so on) may be used and can be adapted to perfectely fit the application.

查看 All Digital Phase Locked Loop 详细介绍:

- 查看 All Digital Phase Locked Loop 完整数据手册

- 联系 All Digital Phase Locked Loop 供应商

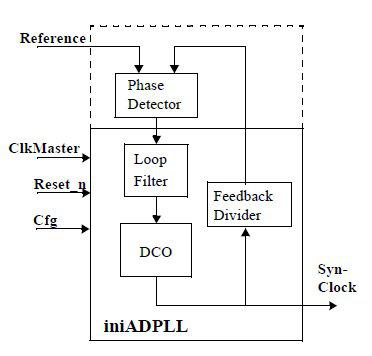

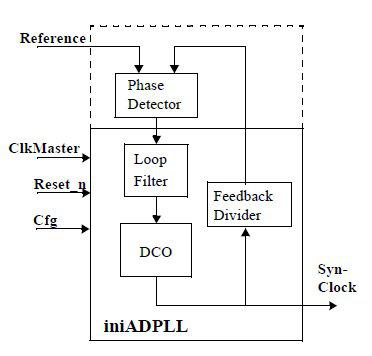

Block Diagram of the All Digital Phase Locked Loop

Digital PLL IP

- Jitter Cleaner PLL Digital Loop Filter

- TSMC GF Intel Low Phase Noise, High-performance Digital LC PLL

- Aeonic Generate Digital PLL for multi-instance, core logic clocking

- 4-GHz Jitter-optimized low-power digital PLL

- 1.5-GHz Jitter-optimized low-power digital PLL

- 4-GHz Jitter-optimized low-power digital PLL