You are here:

AHB Parallel Flash Controller

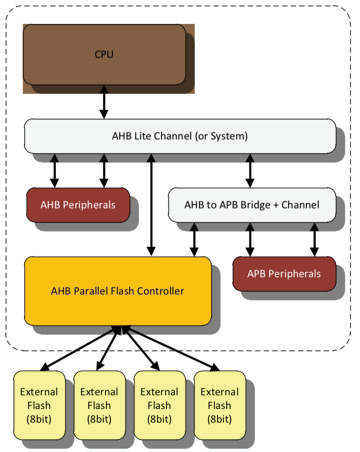

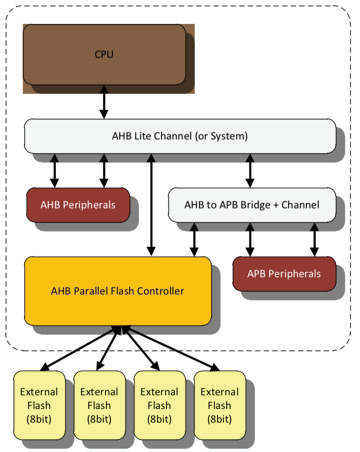

The AHB Parallel Flash Controller allows an AHB Master (usually a CPU) to read, program, or erase the connected arrangement of external parallel SuperFlash devices. The controller implements a set of configuration registers on an APB interface, while Flash accesses occur via an AHB interface. It also implements several modes of operation to facilitate these functions. During normal operation, AHB reads are translated into Flash reads by the controller directly. So, the controller functions as an AHB to Flash Bus Bridge in these instances. Other supported functions, such as Flash program and erase require some software involvement.

The AHB Parallel Flash Controller supports wide range of clock frequencies, timing values for the various Flash transfers can be configured via the APB registers.

The AHB Parallel Flash Controller supports wide range of clock frequencies, timing values for the various Flash transfers can be configured via the APB registers.

查看 AHB Parallel Flash Controller 详细介绍:

- 查看 AHB Parallel Flash Controller 完整数据手册

- 联系 AHB Parallel Flash Controller 供应商

Block Diagram of the AHB Parallel Flash Controller