You are here:

AHB-Lite to AHB-Lite Asynchronous Bridge

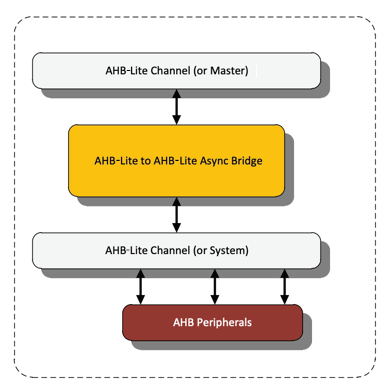

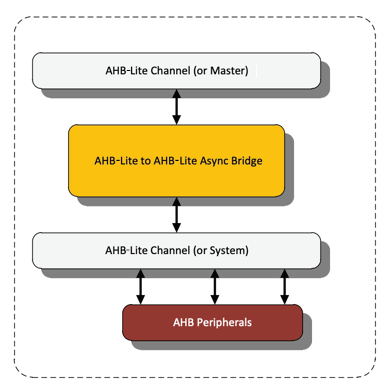

The AHB-Lite to AHB-Lite Asynchronous Bridge translates an AHB-Lite bus transaction (read or write) on one clock domain to an AHB-Lite bus transaction on a second (asynchronous) clock domain. This allows two completely independent AHB-Lite systems to communicate and share data. The bridge is implemented as two state machines - one on the initial or “A” domain and another on the secondary or “B” domain, and several synchronizers. The AHB-Lite to AHB-Lite Asynchronous Bridge acts as an AHB-Lite Slave on the “A” domain, and an AHB-Lite Master on the “B” domain.

查看 AHB-Lite to AHB-Lite Asynchronous Bridge 详细介绍:

- 查看 AHB-Lite to AHB-Lite Asynchronous Bridge 完整数据手册

- 联系 AHB-Lite to AHB-Lite Asynchronous Bridge 供应商

Block Diagram of the AHB-Lite to AHB-Lite Asynchronous Bridge

Bridge IP

- PCIe 5.0 Controller supporting Endpoint, Root Port, Switch, Bridge and advanced features

- PCIe 4.0 Controller supporting Endpoint, Root Port, Switch, Bridge and advanced features

- PCIe Gen3 to SRIO Gen3 Bridge (FPGA)

- RapidIO to AXI Bridge (RAB)

- Digital Capacitive Plus Bridge Sensor Interfaces

- AHB-Lite APB4 Bridge