You are here:

AHB Internal SRAM Controller

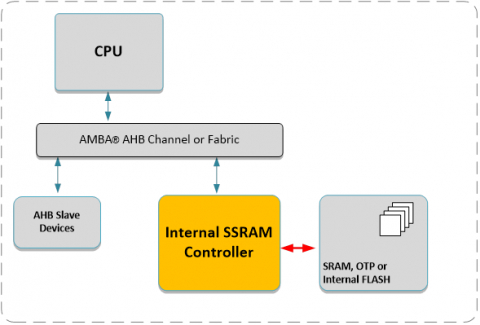

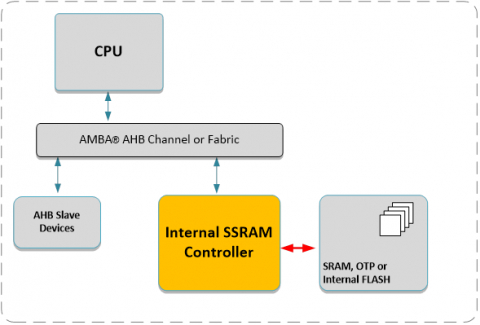

The AHB SRAM Controller provides a standard AHB interface to translate AHB bus reads and writes into reads and writes with the signaling and timing of a standard 32-bit synchronous SRAM.

The AHB SRAM Controller provides zero-wait-state AHB access to the synchronous SRAM in all cases except for the following back-to-back events: an AHB write directly followed by an AHB read. In this case, a single wait state is asserted. Because of the zero-wait-state operation, this interface is intended to drive an on-chip memory (as opposed to off-chip memory where the return path for the read data might require wait states).

The AHB SRAM Controller contains two interfaces: an AHB Slave interface (for connecting to a Mirrored-Slave interface of an AHB Channel module), and a Memory interface (for connecting to a standard synchronous SRAM).

The AHB SRAM Controller provides zero-wait-state AHB access to the synchronous SRAM in all cases except for the following back-to-back events: an AHB write directly followed by an AHB read. In this case, a single wait state is asserted. Because of the zero-wait-state operation, this interface is intended to drive an on-chip memory (as opposed to off-chip memory where the return path for the read data might require wait states).

The AHB SRAM Controller contains two interfaces: an AHB Slave interface (for connecting to a Mirrored-Slave interface of an AHB Channel module), and a Memory interface (for connecting to a standard synchronous SRAM).

查看 AHB Internal SRAM Controller 详细介绍:

- 查看 AHB Internal SRAM Controller 完整数据手册

- 联系 AHB Internal SRAM Controller 供应商

Block Diagram of the AHB Internal SRAM Controller