You are here:

AES-XTS encryption/decryption IP

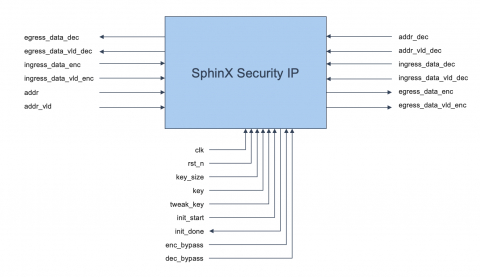

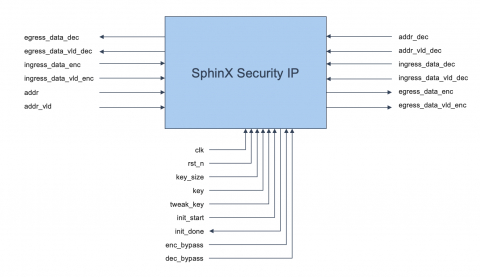

SphinX is designed to accommodate the speed, latency and throughput requirements of high performance computer systems main memory / DRAM. The IP implements the standard (NIST FIPS 197) AES cipher in XTS mode (IEEE Std 1619-2018). The SphinX family of cores covers a scalable IP with 128b and 256b key support, allowing the designer to choose the most efficient and effective core that satisfies the latency and throughput requirements.

The design is fully synchronous and supports independent, non-blocking encryption/decryption at main memory speed. SphinX is available for immediate licensing.

References:

IEEE Std 1619-2018, IEEE Standard for Cryptographic Protection of Data on Block-Oriented Storage Devices https://standards.ieee.org/standard/1619-2018.html

NIST FIPS 197, Advanced Encryption Standard (AES) https://www.nist.gov/publications/advanced-encryption-standard-aes

The design is fully synchronous and supports independent, non-blocking encryption/decryption at main memory speed. SphinX is available for immediate licensing.

References:

IEEE Std 1619-2018, IEEE Standard for Cryptographic Protection of Data on Block-Oriented Storage Devices https://standards.ieee.org/standard/1619-2018.html

NIST FIPS 197, Advanced Encryption Standard (AES) https://www.nist.gov/publications/advanced-encryption-standard-aes

查看 AES-XTS encryption/decryption IP 详细介绍:

- 查看 AES-XTS encryption/decryption IP 完整数据手册

- 联系 AES-XTS encryption/decryption IP 供应商

Block Diagram of the AES-XTS encryption/decryption IP

Cryptography IP

- Secure-IC Securyzr™ Tunable Cryptography solutions with embedded side-channel protections: AES - SHA2 - SHA3 - PKC - RSA - ECC - ML-KEM - ML-DSA - XMSS - LMS - SM2 - SM3 - SM4 - Whirlpool - CHACHA20 - Poly1305

- Post-Quantum Cryptography - xQlave® PQC ML-KEM (Kyber)

- Post-Quantum Cryptography - xQlave® PQC ML-DSA (Dilithium)

- Post-Quantum Cryptography - nQrux® Secure Boot - Quantum-Secure Authenticated Boot (PQC)

- Post-Quantum Cryptography IP: ML-KEM - ML-DSA - XMSS - LMS

- Unified Hardware IP for Post-Quantum Cryptography based on Kyber and Dilithium