You are here:

AES-XTS - Balanced variant

Xiphera's AES symmetric encryption IP cores ensure robust encryption and decryption, providing data confidentiality and integrity with the Advanced Encryption Standard algorithm.These solutions support various AES modes and offer versatile functionality for secure data communication and storage protection. Xiphera’s in-house designed AES encryption engines are optimised for efficiency and high performance in both FPGA and ASIC implementations.

Our AES IP cores offer various modes, ensuring performance, flexibility, and robust security.

Our AES IP cores offer various modes, ensuring performance, flexibility, and robust security.

查看 AES-XTS - Balanced variant 详细介绍:

- 查看 AES-XTS - Balanced variant 完整数据手册

- 联系 AES-XTS - Balanced variant 供应商

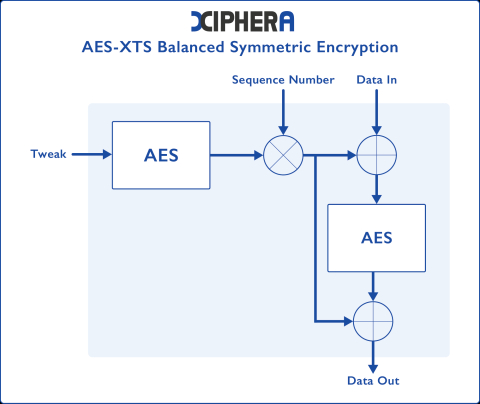

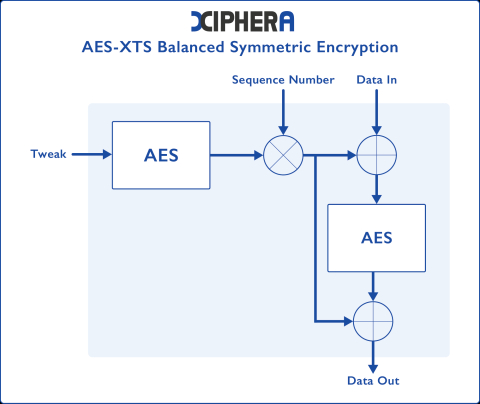

Block Diagram of the AES-XTS - Balanced variant

AES IP

- Secure-IC Securyzr™ Tunable Cryptography solutions with embedded side-channel protections: AES - SHA2 - SHA3 - PKC - RSA - ECC - ML-KEM - ML-DSA - XMSS - LMS - SM2 - SM3 - SM4 - Whirlpool - CHACHA20 - Poly1305

- Secure-IC's Securyzr™ Tunable AES (ECB, CBC, CTR, XTS, CCM, GCM) accelerator - optional SCA protection

- UFS 3.0 Host Controller with AES Encryption compatible with M-PHY 4.0 and UniPro 1.8

- 100G AES Encryption Core

- 10G/25G/40G/50G AES Encryption Core

- 400G AES Encryption Core