You are here:

AES IP Core

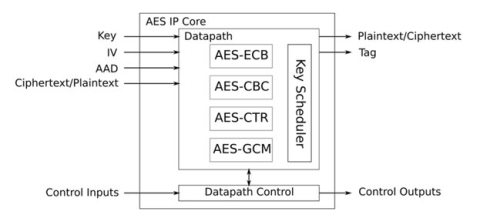

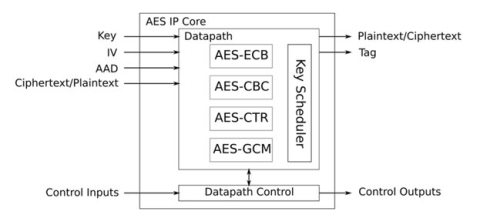

AES IP Core is a Secure Symmetric Block Cipher IP Core that has compliance with the Advanced Encryption Standard (AES) specification in "FIPS 197". This standard specifies the Rijndael algorithm, a symmetric block cipher that can process data blocks of 128 bits, using cipher keys with lengths of 128, 192, and 256 bits.

Countermeasures against side-channel attacks are implemented in the AES IP Core. Procenne AES IP Core is compatible with Xilinx FPGAs and INTEL FPGAs. VHDL is used as the Hardware Description Language of the IP Core. ECB, CBC, CTR, and GCM mode of operations are supported and implemented according to "NIST SP800-38a" and "NIST SP800-38d".

Countermeasures against side-channel attacks are implemented in the AES IP Core. Procenne AES IP Core is compatible with Xilinx FPGAs and INTEL FPGAs. VHDL is used as the Hardware Description Language of the IP Core. ECB, CBC, CTR, and GCM mode of operations are supported and implemented according to "NIST SP800-38a" and "NIST SP800-38d".

查看 AES IP Core 详细介绍:

- 查看 AES IP Core 完整数据手册

- 联系 AES IP Core 供应商

Block Diagram of the AES IP Core

AES IP

- Secure-IC Securyzr™ Tunable Cryptography solutions with embedded side-channel protections: AES - SHA2 - SHA3 - PKC - RSA - ECC - ML-KEM - ML-DSA - XMSS - LMS - SM2 - SM3 - SM4 - Whirlpool - CHACHA20 - Poly1305

- Secure-IC's Securyzr™ Tunable AES (ECB, CBC, CTR, XTS, CCM, GCM) accelerator - optional SCA protection

- UFS 3.0 Host Controller with AES Encryption compatible with M-PHY 4.0 and UniPro 1.8

- 100G AES Encryption Core

- 10G/25G/40G/50G AES Encryption Core

- 400G AES Encryption Core