You are here:

AES Engine IP (silicon proven)

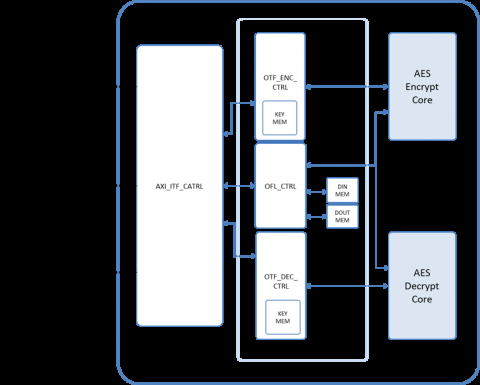

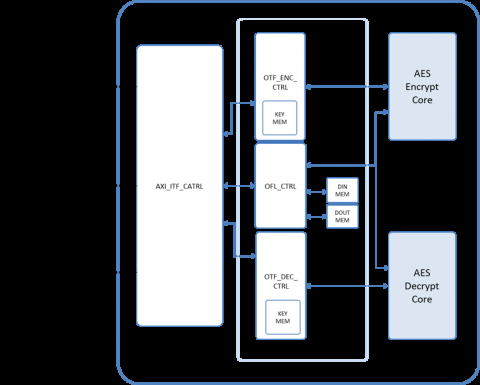

YEESTOR's AES engine (ESAES) IP is a high-performance cryptographic engine operates in AES (Rijndael) NIST Federal information processing standard FIPS-197. It supports AES-ECB AES-XTS mode and 128/256 key-length both encryption/decryption. The core engine supports 128/256/512 data width operation. The encryption and decryption engines are-full duplex to provide high performance and support on-the-fly key update. ESAES is delivered with complete development package for the ease of use in both FPGA and SoC design.

查看 AES Engine IP (silicon proven) 详细介绍:

- 查看 AES Engine IP (silicon proven) 完整数据手册

- 联系 AES Engine IP (silicon proven) 供应商

Block Diagram of the AES Engine IP (silicon proven)

AES IP

- Secure-IC Securyzr™ Tunable Cryptography solutions with embedded side-channel protections: AES - SHA2 - SHA3 - PKC - RSA - ECC - ML-KEM - ML-DSA - XMSS - LMS - SM2 - SM3 - SM4 - Whirlpool - CHACHA20 - Poly1305

- Secure-IC's Securyzr™ Tunable AES (ECB, CBC, CTR, XTS, CCM, GCM) accelerator - optional SCA protection

- UFS 3.0 Host Controller with AES Encryption compatible with M-PHY 4.0 and UniPro 1.8

- 100G AES Encryption Core

- 10G/25G/40G/50G AES Encryption Core

- 400G AES Encryption Core