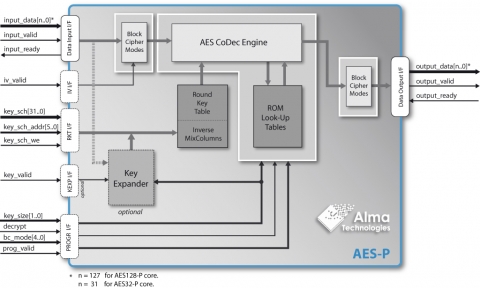

AES Encryption & Decryption with Programmable Block-Cipher Mode

The AES-P core is available in two variations, the standard AES32-P and the fast AES128-P: AES32-P has a 32-bit internal datapath, while the AES128-P uses 128-bit datapath. The AES32-P is more compact in size, but offers a lower throughput than the AES128-P. The AES32-P needs 44/52/60 clock cycles to encrypt or decrypt an input block using 128/192/256-bit cipher-key, respectively, while only 11/13/15 clock cycles are required for the same by the AES128-P core.

During each step of the encryption or decryption processing the core requires a previously calculated Round Key Value, derived from the cipher-key using a key expansion algorithm. The Round Key Values must be stored to the internal Round Key Table, from which the core retrieves the appropriate one for each processing step. Alternatively, instead of directly programming the Round Key Values to the Round Key Table, an optional Key Expander module can be provided. This module automatically calculates the Round Key Values and fills the internal Round Key Table according to the cipher-key given to the core.

The AES-P core is equipped with easy-to-use fully stallable interfaces for both input and output. These are designed to permit the user application to pause the produced output data stream when it is not able to receive data, or to pause the input stream towards the core according to data arrival rate.

查看 AES Encryption & Decryption with Programmable Block-Cipher Mode 详细介绍:

- 查看 AES Encryption & Decryption with Programmable Block-Cipher Mode 完整数据手册

- 联系 AES Encryption & Decryption with Programmable Block-Cipher Mode 供应商

Block Diagram of the AES Encryption & Decryption with Programmable Block-Cipher Mode

AES IP

- Secure-IC Securyzr™ Tunable Cryptography solutions with embedded side-channel protections: AES - SHA2 - SHA3 - PKC - RSA - ECC - ML-KEM - ML-DSA - XMSS - LMS - SM2 - SM3 - SM4 - Whirlpool - CHACHA20 - Poly1305

- Secure-IC's Securyzr™ Tunable AES (ECB, CBC, CTR, XTS, CCM, GCM) accelerator - optional SCA protection

- UFS 3.0 Host Controller with AES Encryption compatible with M-PHY 4.0 and UniPro 1.8

- 100G AES Encryption Core

- 10G/25G/40G/50G AES Encryption Core

- 400G AES Encryption Core